# FABRICATION AND CHARACTERIZATION OF VERTICAL SILICON NANOWIRE ARRAYS: A PROMISING BUILDING BLOCK FOR THERMOELECTRIC DEVICES

## **A DISSERTATION**

SUBMITTED TO THE DEPARTMENT OF MECHANICAL

**ENGINEERING**

AND THE COMMITTEE ON GRADUATE STUDIES

OF STANFORD UNIVERSITY

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

Jeffrey M. Weisse

August 2013

## © 2013 by Jeffrey Michael Weisse. All Rights Reserved. Re-distributed by Stanford University under license with the author.

This work is licensed under a Creative Commons Attribution-Noncommercial 3.0 United States License. http://creativecommons.org/licenses/by-nc/3.0/us/

This dissertation is online at: http://purl.stanford.edu/hb665nr7892

| I certify that I have read this dissertation and that, in my opinion, it is fully adequa | te |

|------------------------------------------------------------------------------------------|----|

| in scope and quality as a dissertation for the degree of Doctor of Philosophy.           |    |

## Xiaolin Zheng, Primary Adviser

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

**Kenneth Goodson**

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

**Beth Pruitt**

Approved for the Stanford University Committee on Graduate Studies.

Patricia J. Gumport, Vice Provost for Graduate Education

This signature page was generated electronically upon submission of this dissertation in electronic format. An original signed hard copy of the signature page is on file in University Archives.

## **ABSTRACT**

Thermoelectric devices, which convert temperature gradients into electricity, have the potential to harness waste heat to improve overall energy efficiency. However, current thermoelectric devices are not cost-effective for most applications due to their low efficiencies and high material costs. To improve the overall conversion efficiency, thermoelectric materials should possess material properties that closely resemble a "phonon glass" and an "electron crystal". The desired low thermal and high electrical conductivities allow the thermoelectric device to maintain a high temperature gradient while effectively transporting current. Unfortunately, thermal transport and electrical transport are a closely coupled phenomena and it is difficult to independently engineer each specific conduction mechanism in conventional materials. One strategy to realize this is to generate nanostructured silicon (e.g. silicon nanowires (SiNWs)), which have been shown to reduce thermal conductivity ( $\kappa$ ) through enhanced phonon scattering while theoretically preserving the electronic properties; therefore, improving the overall device efficiency.

The ability to suppress phonon propagation in nanostructured silicon, which has a bulk phonon mean free path  $\sim 300$  nm at 300 K, has raised substantial interest as an ultralow  $\kappa$  material capable of reducing the thermal conductivity up to three orders of magnitude lower than that of bulk silicon. While the formation of porous silicon and SiNWs has individually been demonstrated as promising methods to reduce  $\kappa$ , there is a

lack of research investigating the thermal conductivity in SiNWs containing porosity. We fabricated SiNW arrays using top-down etching methods (deep reactive ion etching and metal-assisted chemical etching) and by tuning the diameter with different patterning methods and tuning the internal porosity with different SiNW etching conditions. The effects of both the porosity and the SiNW dimensions at the array scale are investigated by measuring  $\kappa$  of vertical SiNW arrays using a nanosecond time-domain thermoreflectance technique.

In addition to thermoelectric devices, vertical SiNW arrays, due to their anisotropic electronic and optical properties, large surface to volume ratios, resistance to Li-ion pulverization, ability to orthogonalize light absorption and carrier transport directions, and trap light, make vertical SiNW arrays important building blocks for various applications. These may include sensors, solar cells, and Li-ion batteries. Many of these applications benefit from vertical SiNW arrays fabricated on non-silicon based substrates which endow the final devices with the properties of flexibility, transparency, and light-weight while removing any performance limitation of the silicon fabrication substrate.

We then developed two vertical transfer printing methods (V-TPMs) that are used to detach SiNW arrays from their original fabrication substrates and subsequently attach them to any desired substrate while retaining their vertical alignment over a large area. The transfer of vertically aligned arrays of uniform length SiNWs is desirable to remove

the electrical, thermal, optical, and structural impact from the fabrication substrate and also to enable the integration of vertical SiNWs directly into flexible and conductive substrates. Moreover, realization of a thermoelectric device requires the formation of electrical contacts on both sides of the SiNW arrays. We formed metallic contacts on both ends of the SiNW arrays with a mechanical supporting and electrical insulating polymer in between. Electrical characterization of the SiNW devices exhibited good current-voltage (I-V) characteristics independent of substrates materials and bending conditions. We believe the V-TPMs developed in this work have great potential for manufacturing practical thermoelectric devices as well as high performing, scalable SiNW array devices on flexible and conducting substrates.

## **ACKNOWLEDGEMENTS**

First and foremost, I would like to express my most genuine appreciation to my principle advisor, Professor Xiaolin Zheng for her continuous support, supervision, and guidance during my academic journey. Dr. Zheng provided endless encouragement, patience, creativity and knowledge during my Ph.D which helped me develop both as a researcher and as a person. Working with Dr. Zheng has been a truly amazing experience that will have a lasting impact on the rest of my life.

I would like to thank Professor Beth Pruitt for her guidance over the years. Dr. Pruitt was one of the first professors that I knew at Stanford and I thoroughly enjoyed her introduction to MEMS class, for which I was fortunate enough to be the TA the following year. Working directly with Dr. Pruitt as her TA was a tremendous and rewarding experience that I am truly grateful for. I would also like to thank Professor Ken Goodson for his collaboration and inspiration over the years. Dr. Goodson always provided immense encouragement and motivation to test the limits and potential of my research. I also thank my dissertation committee members, Professors Thomas Kenny and Debbie Senesky for their insightful comments and valuable time.

I cannot thank my fellow group members enough for their support and encouragement over the past six years: Dr. Dong Rip Kim, Chi Hwan Lee, Dr. Pratap, Rao, Dr. Yunzhe Feng, Dr. Insun Cho, Yuma Ohkura, Dr. Hong Li, Lili Cai, and Runlai Luo. Everyone has been instrumental in my research and I have thoroughly enjoyed working with and have learned from everyone in the Zheng group.

I am extremely grateful for everyone who has impacted my research while at Stanford. MERL has been a wonderful place to do research and would like to especially thank the Goodson, Pruitt, Levenston and Santiago group members for their advice and friendships over the years. In particular, I would like to give special thanks to Dr. Amy Marconnet, Michael Barako, Shilpi Roy, and Dr. Matthew Panzer for their friendship and collaborations. I am also greatly appreciative of all the help and guidance I received from the staff members at the Stanford Nanofabrication Facility and the Stanford Nano Center.

I am truly grateful for the number of California friends that have supported me and made my graduate life an amazing experience. Thank you for all of the amazing memories, endless summer activities, and winters in Tahoe.

Last but certainly not least, I would like to thank my family for their endless support and love. I certainly would not be the person I am today without the support from my parents, Tom and Ann. They have supported me in every way possible over the years and I cannot express how thankful I am and how much it means to me to have them as my parents. I also thank my brother, Bob, and my sister-in-law, Katherine, for their love and support. I give a special thanks to my wonderful fiancée, Melissa, who has provided me with endless love, support, and encouragement along this long journey. This thesis is dedicated to all my family members.

# TABLE OF CONTENTS

| ABSTRACT           |                                           | iv          |

|--------------------|-------------------------------------------|-------------|

| TABLE OF CONTEN    | NTS                                       | ix          |

| LIST OF TABLES     |                                           | xiv         |

| LIST OF FIGURES    |                                           | XV          |

|                    |                                           |             |

|                    |                                           |             |

| Chapter 1. Introdu | ection                                    | 1           |

| 1.1. Motivation    |                                           | 1           |

| 1.2. Background    | on Thermoelectrics                        | 4           |

| 1.2.1. The The     | ermoelectric Theory                       | 4           |

| 1.2.2. State-of    | the-Art Thermoelectric Materials          | 9           |

| 1.2.3. Potentia    | l of Nanostructured Silicon               | 13          |

| 1.3. Opportunitie  | es and Challenges                         | 16          |

| 1.3.1. Vertical    | Si Nanowire Array Based Thermoelectric I  | Devices16   |

| 1.3.2. Addition    | nal Vertical Si Nanowire Arrays Based App | lications17 |

| 1.4 Scope and O    | prognization of Thesis                    | 19          |

| Chapter 2. | <b>Experimental Nanostructured Silicon Fabrication Methods</b> | 21 |

|------------|----------------------------------------------------------------|----|

| 2.1. Poi   | ous Silicon Formation: Etching Chemistry and Theory            | 22 |

| 2.1.1.     | Anodization                                                    | 23 |

| 2.1.2.     | Electropolishing                                               | 26 |

| 2.1.3.     | Stain Etching                                                  | 29 |

| 2.2. To    | p-Down Non-porous Silicon Wire Formation                       | 30 |

| 2.2.1.     | Deep Reactive Ion Etching                                      | 30 |

| 2.2.2.     | Nanosphere Lithography                                         | 32 |

| 2.2.3.     | Silica Sphere Creation and Functionalization                   | 35 |

| 2.3. Me    | tal-Assisted Chemical Etching                                  | 38 |

| 2.3.1.     | Etching Mechanism Theory                                       | 39 |

| 2.3.2.     | Catalyst Patterning Methods                                    | 41 |

| 2.3.3.     | Control Over The SiNW Morphology and Geometry                  | 44 |

| 2.4. Top   | p-down Silicon Nanowire Diameter Reduction                     | 49 |

| 2.5. Sec   | etion Conclusion                                               | 52 |

| Chapte | r 3. Thermal Conductivity Trends in SiNW Arrays5                      | 3 |

|--------|-----------------------------------------------------------------------|---|

| 3.1.   | Background5                                                           | 3 |

| 3.2.   | Fabrication Methodology5                                              | 4 |

| 3.3.   | Nanosecond Transient Thermoreflectance (TTR)5                         | 7 |

| 3.4.   | Results6                                                              | О |

| 3.4    | .1. Large Diameter SiNW Trends ( $d > \lambda_{bulk\_Si}$ )6          | О |

| 3.4    | .2. Small Diameter SiNW Trends ( $d < \lambda_{bulk\_Si}$ )6          | 3 |

| 3.4    | .3. Estimated Electrical Performance6                                 | 4 |

| 3.5.   | Section Conclusion6                                                   | 8 |

|        |                                                                       |   |

| Chapte | r 4. Transfer of Uniform Silicon Nanowire Arrays via Crack Formation6 | 9 |

| 4.1.   | Background6                                                           | 9 |

| 4.2.   | Controlled Separation of Uniform Length SiNW Arrays7                  | О |

| 4.3.   | Crack Formation Theory                                                | 2 |

| 4.4.   | Basic Functionalities                                                 | 5 |

| 4.5.   | Section Conclusion                                                    | 2 |

| Chapte                                                        | r 5. Fabrication of Flexible and Vertical Silicon Nanowire Electronics                | .84                    |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------|

| 5.1.                                                          | Background                                                                            | .84                    |

| 5.2.                                                          | Fabrication Methodology                                                               | .85                    |

| 5.3.                                                          | Marginally-porous SiNW Devices                                                        | .89                    |

| 5.4.                                                          | Porous SiNW Devices                                                                   | .91                    |

| 5.5.                                                          | Axially-Modulated SiNW Devices                                                        | .94                    |

| 5.6.                                                          | Section Conclusion                                                                    | .96                    |

|                                                               |                                                                                       |                        |

|                                                               |                                                                                       |                        |

|                                                               |                                                                                       |                        |

| Chapte                                                        | r 6. Electro-assisted Transfer for Vertical Silicon Wire Arrays                       | .97                    |

| Chapte 6.1.                                                   | r 6. Electro-assisted Transfer for Vertical Silicon Wire Arrays                       |                        |

|                                                               |                                                                                       | .97                    |

| 6.1.                                                          | Background                                                                            | .97<br>.98             |

| 6.1.<br>6.2.                                                  | Background  Fabrication Methodology                                                   | 97<br>98<br>100        |

| <ul><li>6.1.</li><li>6.2.</li><li>6.3.</li></ul>              | Background  Fabrication Methodology  Controlled Location for Porous Silicon Formation | 97<br>98<br>100<br>103 |

| <ul><li>6.1.</li><li>6.2.</li><li>6.3.</li><li>6.4.</li></ul> | Background                                                                            | 97<br>98<br>100<br>103 |

| Chapter 7.   | Conclusion                                                           |

|--------------|----------------------------------------------------------------------|

| 7.1. Con     | cluding Remarks                                                      |

| 7.2. Reco    | ommendation for Future Work                                          |

| 7.2.1.       | Optimization of Electrical Contacts                                  |

| 7.2.2.       | Integrated Electrical and Thermal Conductivity Measurement121        |

| 7.2.3.       | Optimization of Nanostructured Silicon                               |

| 7.2.4.       | Fabrication of a Functional Thermoelectric Device and other Relevant |

| Applicat     | ions                                                                 |

|              |                                                                      |

| Appendix A:  | Porous Si and Electropolishing Procedures                            |

| Appendix B:  | Fabrication Procedure for DRIE Si Microwires and Nanowires130        |

| Appendix C:  | General Fabrication Recipe used to synthesis 650 nm spheres133       |

| Appendix D:  | Functionalization of Silica Spheres with APTES135                    |

| Appendix E:  | Fabrication of SiNWs with Varied Diameter and Porosity137            |

| Appendix F:  | Error Analysis for the Vertical SiNW Array Thermal Conductivity141   |

| Appendix G:  | Matlab Code use to Determine to SiNW Volume Fraction145              |

| Appendix H:  | Error Analysis of the Vertical SiNW Array Porosity146                |

| Bibliography | 150                                                                  |

## LIST OF TABLES

| Table 1. Su        | ummary of SiNW arrays with varied diameters and porosities                   |

|--------------------|------------------------------------------------------------------------------|

| Table 2. A         | verage porosities and thermal conductivities for large diameter MACE         |

| sa                 | amples67                                                                     |

| Table 3. V         | Values and tolerances of the measured film thermal conductivity, volume      |

| fr                 | faction, and literature value for the parylene thermal conductivity          |

| Table 4. E         | Error propagation analysis used to determine the overall error in the SiNW   |

| th                 | nermal conductivity values                                                   |

| Table 5. M         | leasured values and calculated porosity of SiNW used for thermal             |

| ch                 | naracterization                                                              |

| <b>Table 6.</b> Fi | ixed estimated error values for measured values used to determine SiNW array |

| po                 | prosity                                                                      |

| Table 7. E         | rror propagation analysis used to determine the overall uncertainty in the   |

| Si                 | iNW porosity values149                                                       |

# LIST OF FIGURES

| <b>Figure 1-1.</b> Relative efficiency and possible applications of thermoelectric materials 4                 |

|----------------------------------------------------------------------------------------------------------------|

| <b>Figure 1-2</b> . Schematic illustrating a representative thermoelectric device                              |

| Figure 1-3. Representative illustration of the dependence of zT, $\alpha$ , $\sigma$ , and $\kappa$ on carrier |

| concentration and lattice thermal conductity9                                                                  |

| Figure 1-4. Summary of promising thermoelectric materials and their relative element                           |

| abundance12                                                                                                    |

| Figure 1-5. Schematic illustrating the electron and phonon transport in nanostructured Si.                     |

|                                                                                                                |

| <b>Figure 2-1.</b> Cross-sectional schematic of an anodization cell used to form porous Si 24                  |

| Figure 2-2. Reaction model for the anodic dissolution of Si in the presence of                                 |

| hydrofluoric acid                                                                                              |

| Figure 2-3. Reaction model and schematic of the anodic dissolution of Si during porous                         |

| Si formation and electropolishing                                                                              |

| <b>Figure 2-4.</b> Exemplary current density vs. voltage curve for a Si wafer                                  |

| Figure 2-5. SEM images of microwires and nanowire arrays formed by the DRIE                                    |

| process. 32                                                                                                    |

| Figure 2-6. Schematic of the Langmuir Blodgett Trough used to deposit a monolayer of                           |

| silica spheres for nanosphere lithography                                                                      |

| Figure 2-7. SEM images of polystyrene spheres etched in O <sub>2</sub> plasma and silica spheres               |

| etched in a fluorine-based plasma                                                                              |

| Figure 2-8. SEM images of a monolayer of silica sphere with diameters of (a) 175 nm,                           |

| (b) 650 nm and (c) 2 μm                                                                                        |

| Figure 2-9. Schematic of hydroxyl terminated and amino group terminated silica sphere        |

|----------------------------------------------------------------------------------------------|

|                                                                                              |

| Figure 2-10. Overview of MACE including, the electrochemical potential of typical            |

| metal catalysts, the reactions occurring during MACE and the bone                            |

| orientation for the three common crystal planes in Si                                        |

| Figure 2-11. SEM images of SiNWs formed with MACE when the silver is patterned               |

| with silver salts and with nanosphere lithography                                            |

| Figure 2-12. Schematic demonstrating the SiNW formation process under a variety of           |

| parameters that affect the SiNW porous morphology 4"                                         |

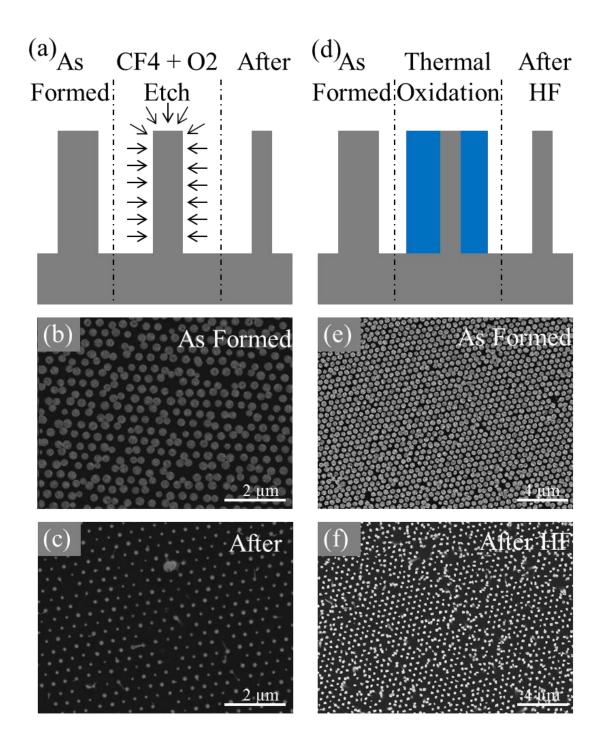

| Figure 2-13. Top-down SiNW diameter reduction methods                                        |

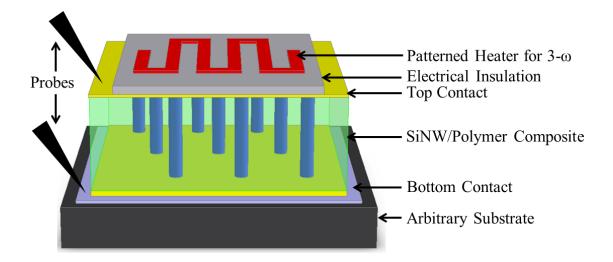

| Figure 3-1. Fabrication of the vertically aligned SiNW arrays for the nanosecond             |

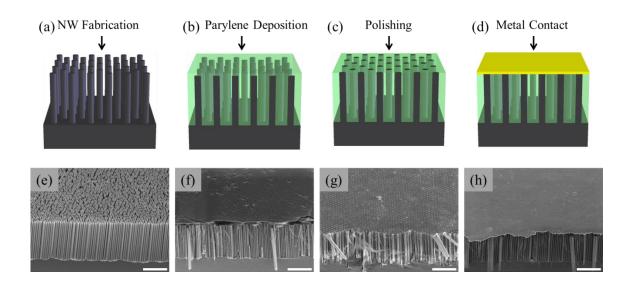

| thermoreflectance measurements                                                               |

| <b>Figure 3-2</b> . Representative illustration of nanosecond transient thermoreflectance 58 |

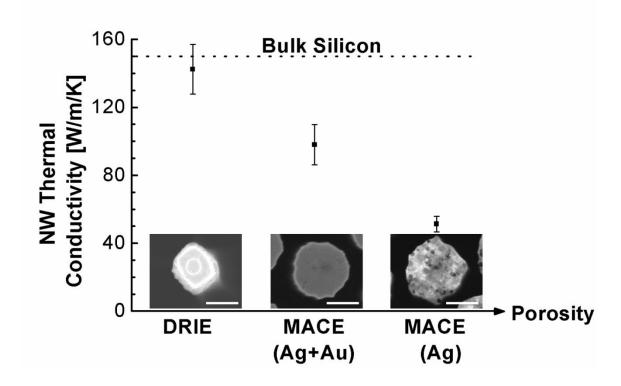

| Figure 3-3. Thermal conductivity of large-diameter SiNWs with varied etching method          |

| 6                                                                                            |

| Figure 3-4. Thermal conductivity of large-diameter non-porous and porous SiNW array          |

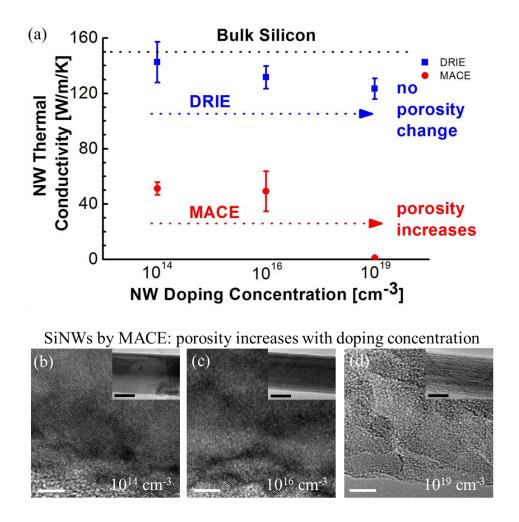

| as a function of doping concentration                                                        |

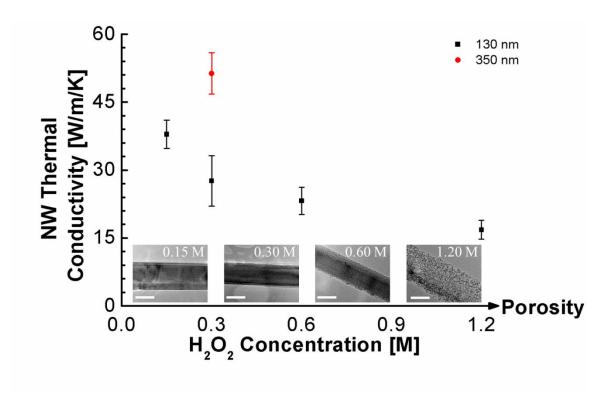

| Figure 3-5. Thermal conductivity of small-diameter (approximately 130 nm) SiNW               |

| $(10^{14} \mathrm{cm}^{-3})$ as a function of porosity                                       |

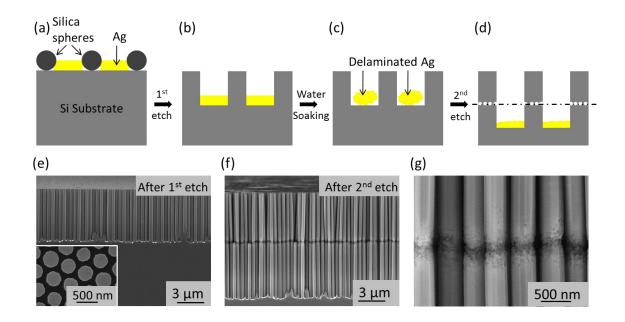

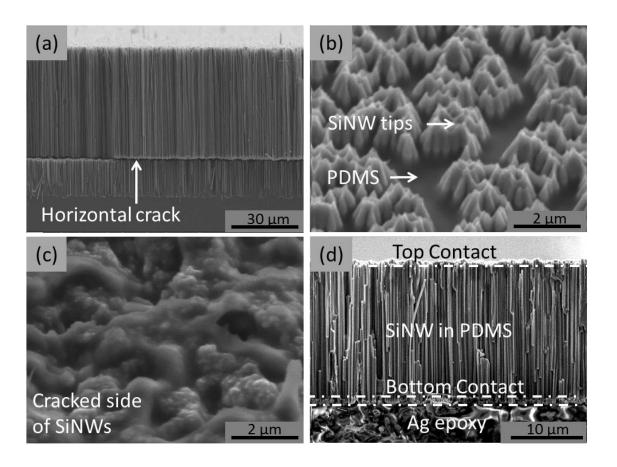

| <b>Figure 4-1.</b> Schematic of the fabrication procedure for the cracked SiNW array 72      |

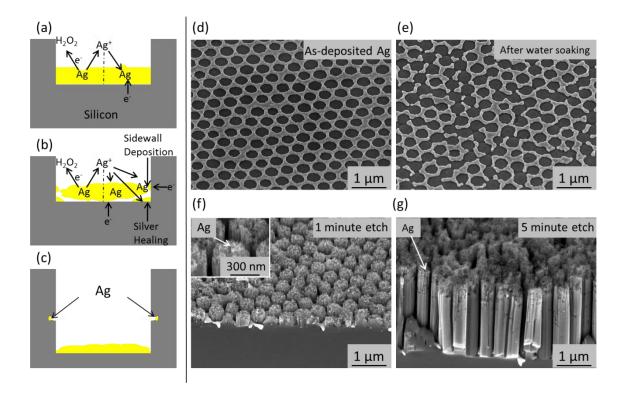

| Figure 4-2. The crack formation mechanism. the Si wafer while the SiNWs continue to          |

| elongate75                                                                                   |

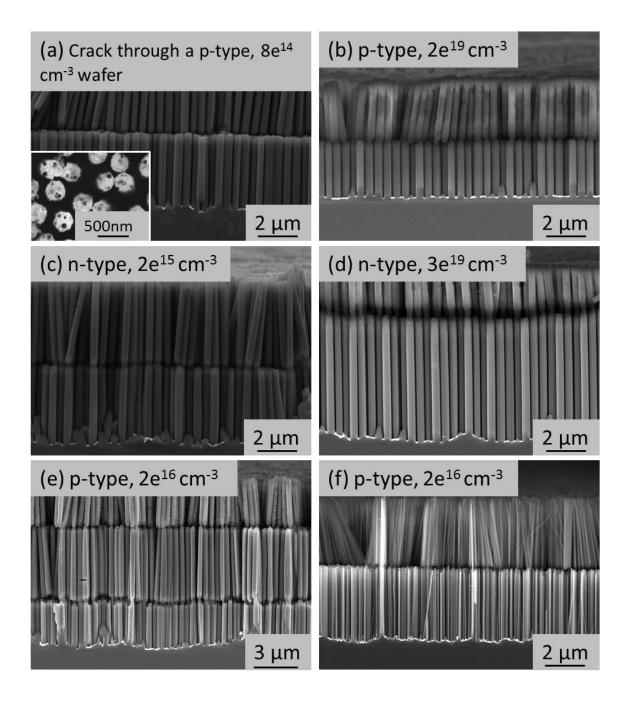

| <b>Figure 4-3.</b> Generality of the crack formation.                                        |

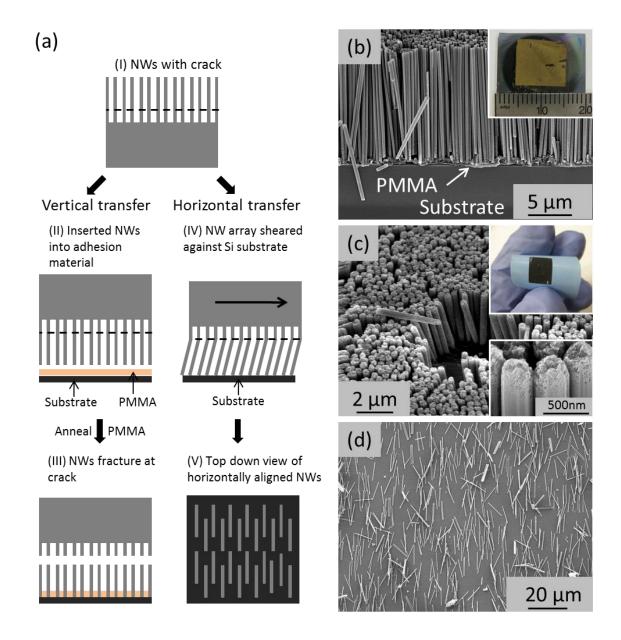

| Figure 4-4. Transfer of the cracked SiNWs.                                 | 80                     |

|----------------------------------------------------------------------------|------------------------|

| Figure 4-5. Schematic and SEM image of embedding vertically align          | ned SiNWs in PDMS      |

| and along the base of a trench.                                            | 82                     |

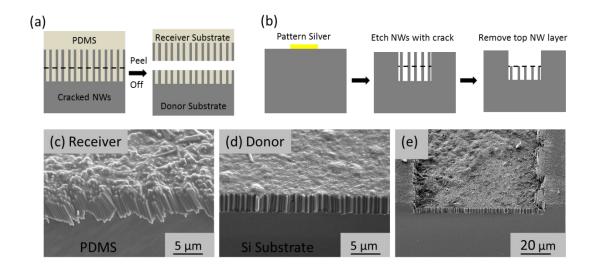

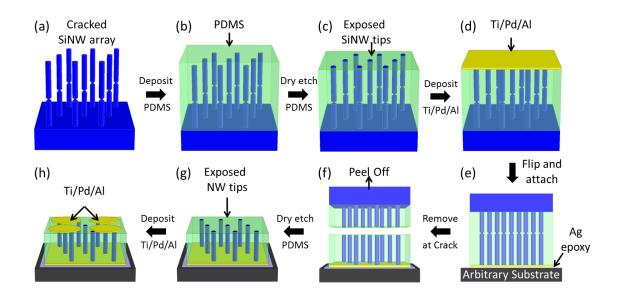

| Figure 5-1. Schematic of the fabrication procedure for vertical Si         | NW array electronic    |

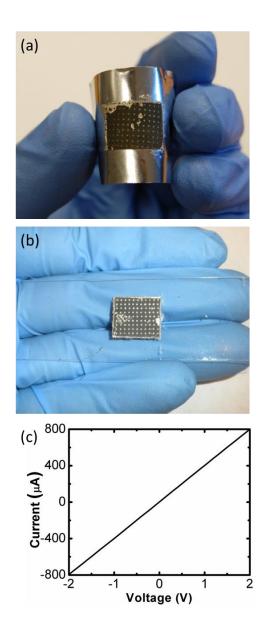

| devices on non-Si based substrates with the crack-assiste                  | d V-TPM 87             |

| Figure 5-2. SEM images of various steps during the fabrication of          | vertical SiNW array    |

| electronic devices.                                                        | 88                     |

| Figure 5-3. Optical images and I-V curves of vertical maginally-p          | orous SiNW devices     |

| fabricated arbituary substrates                                            | 90                     |

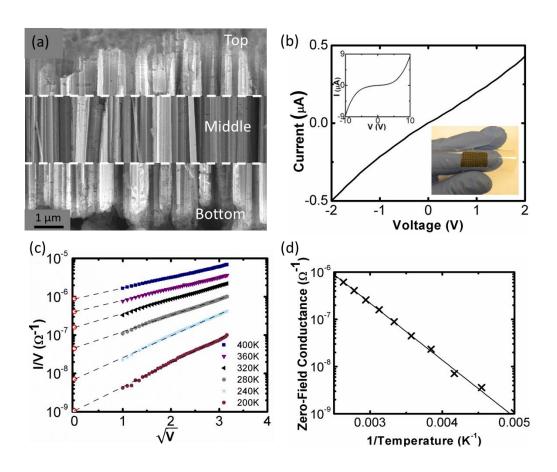

| Figure 5-4. Cross sectional SEM images and I-V curve of a vertical         | porous SiNW device     |

| fabricated on a arbituary substrates that follow the Poo                   | ole-Frenkel transport  |

| relation                                                                   | 93                     |

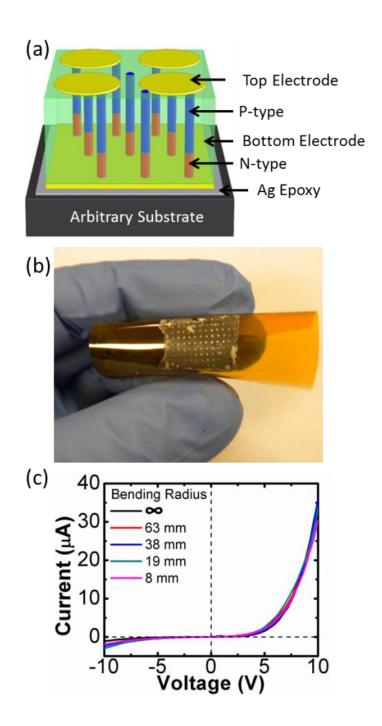

| Figure 5-5. Schematic and optical image of axially-modulated vert          | ical p-n SiNW array    |

| devices fabricated on a Kapton sheet.                                      | 95                     |

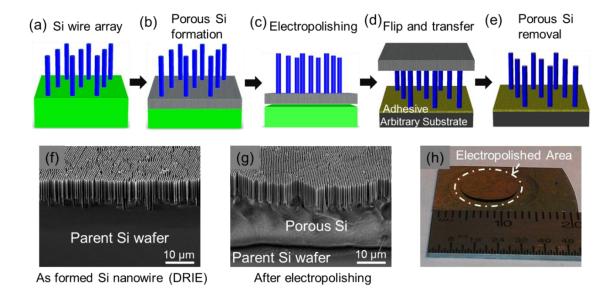

| Figure 6-1. Schematic of the electro-assisted transfer of vertical Si w    | ire arrays 100         |

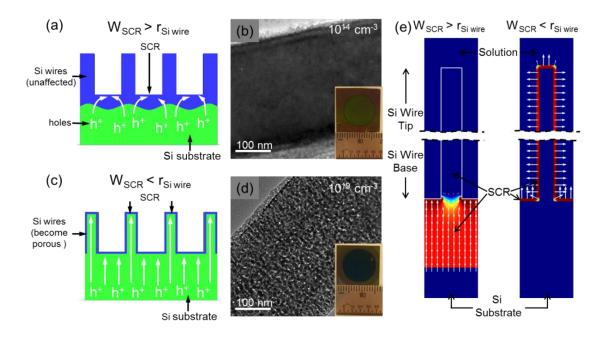

| Figure 6-2. The location of the space-charge region determines th          | e distribution of the  |

| electric field and therefore the location of the porous Si f               | ormation 102           |

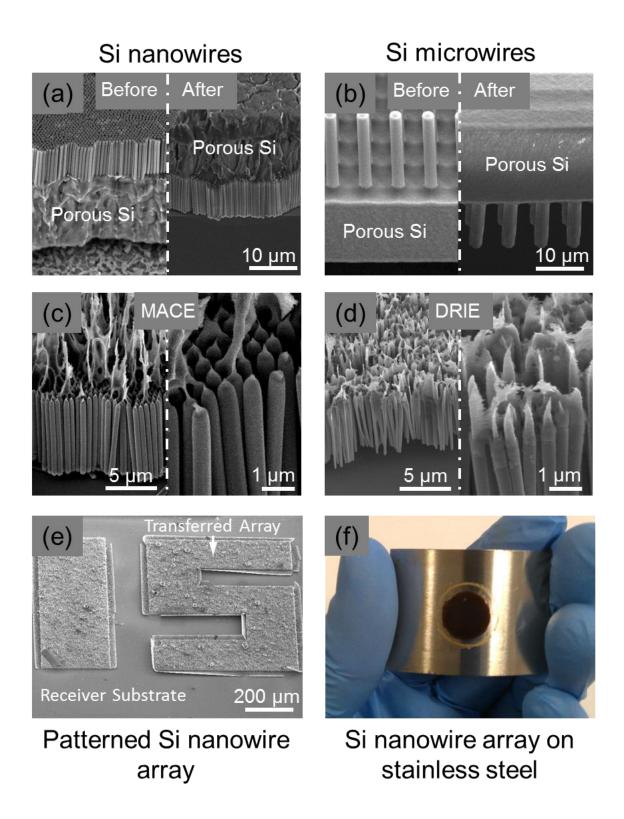

| Figure 6-3. Generality of the electro-assisted transfer method in transfer | nsferring different Si |

| wires to other substrates                                                  | 106                    |

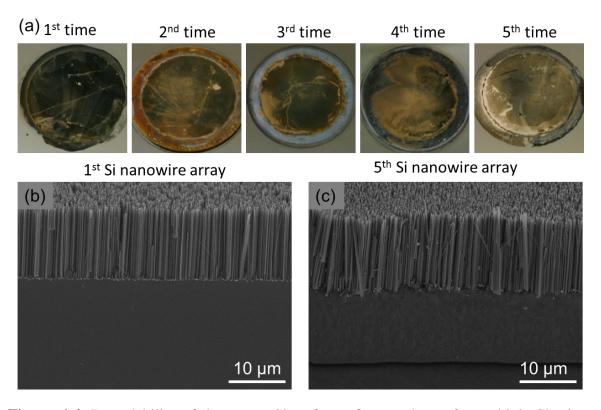

| Figure 6-4. Recyclability of the parent Si wafer to form and trans         | fer multiple Si wire   |

| arrays from a single substrate                                             | 107                    |

| <b>Figure 6-5.</b> Comparison of the electrical conductivity of Si nanowires before (as-etched) |

|-------------------------------------------------------------------------------------------------|

| and after the porous Si layer is formed underneath the Si nanowire array.                       |

|                                                                                                 |

| Figure 6-6. Schematic of the fabrication procedure for the electro-assisted transfer for Si     |

| nanowire for integration into electrical devices                                                |

| Figure 6-7. Synthesis of Si nanowires by the current-induced MACE for which the                 |

| oxidizer, H <sub>2</sub> O <sub>2</sub> is replaced by an applied current                       |

| Figure 7-1. Rough estimation of zT values at room temperature based on SiNW arrays              |

| characterized in this thesis                                                                    |

| Figure 7-2. Schematic of measurement setup capable of simultaneously measuring the              |

| thermal and electrical conductivity                                                             |

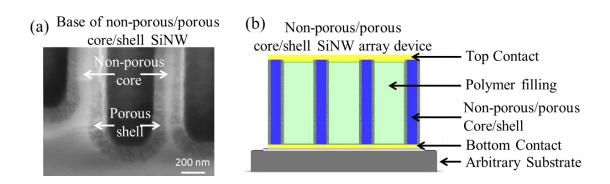

| <b>Figure 7-3.</b> Fabrication of non-porous/porous core/shell SiNW arrays                      |

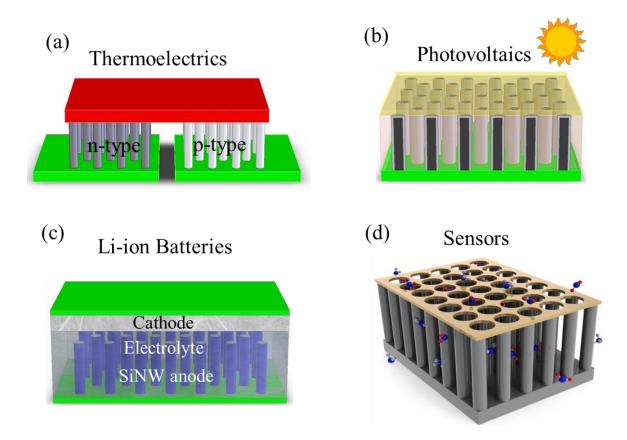

| Figure 7-4. Schematic of some potential applications that could be improved with the            |

| methods developed within this thesis                                                            |

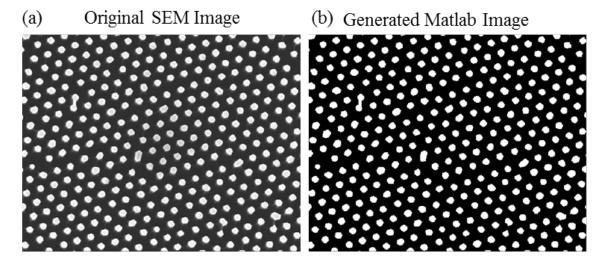

| Figure G-1. Example of an SEM image that is converted to a Matlab generated black and           |

| white image used for determining the volume fraction                                            |

## **Chapter 1. Introduction**

### 1.1. Motivation

Prior to the industrial revolution, the world population growth and natural resource consumption were relatively insignificant compared to what they are today. This started to change with the invention of the steam engine and continued with the development of the internal combustion engine. These engines allowed society to transport and move goods efficiently around the world, sparking the future for rapid technological development and consumption of our natural resources [1]. Again in the mid-twentieth century, society hit another monumental landmark with the invention of the transistor. Since then, the number of transistors on an integrated circuit has been growing at an exponential rate, almost doubling every two years. This has led technology to grow at an unprecedented rate. Developed countries are continuing to make technology faster, cheaper and smaller, allowing individuals to consume more than ever. At the same time, modern technology is becoming available to non-developed countries, who can now gain access to electricity and health care, drastically improving their quality of life and life expectancy, resulting in a rapid increase in the population of the world. combination of the rapid population growth and increased power consumption has had a severe impact on the pollution of our planet and the depletion of our natural resources. In order to further mitigate these risks, society needs to adopt clean energy technologies to replace the technologies consuming our natural resources while still meeting the demands from society [1].

The demand to improve efficiency in current systems is also highly desired. Thermoelectric devices, which are solid-state energy harvesting devices capable of converting a temperature gradient into an electrical voltage, offer the potential to achieve this goal. Currently, heat engines are used to produce ~90% of the world's energy in a useful form, of which ~60% is lost to the environment as waste heat, opening up promising opportunities for thermoelectric devices [2]. For example, a typical automobile has an efficiency of 20-25% due to the production of waste heat, of which the majority is expelled in the exhaust and radiator [2, 3]. The waste heat from the exhaust or radiator could be harvested with a thermoelectric device to convert this energy back into useful electricity, which would reduce the mechanical load placed on the alternator and increase the overall engine efficiency. The gas mileage would increase, allowing automobiles to be manufactured with smaller engines that would require less power.

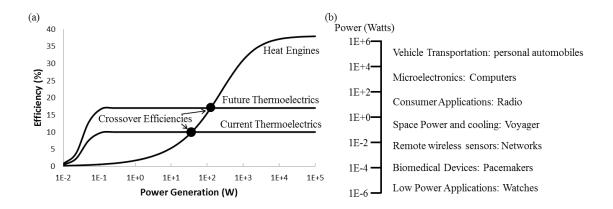

Thermoelectrics have characteristic traits that make them promising in many applications. For example, typical heat engines become less efficient as they are scaled down, while thermoelectric devices maintain a relatively stable efficiency over a wider range of power generation levels, opening up opportunities for thermoelectrics in low power (< 1 kW) applications [4]. Figure 1-1a shows a representative illustration of the low power regime where the thermoelectric efficiency is more efficient than conventional heat engines [4]. The range of power levels where thermoelectrics are more efficient will only increase as the efficiency of thermoelectric materials continues to improve. Furthermore, the demand for systems capable of supplying small amounts of power is becoming more important as technology is allowing devices to decrease in size and

increase in performance. Examples of applications that fall into this range are shown in Figure 1-1b [5]. In addition, most of these applications require the devices to be wireless, portable, and long lasting: this mandates an onboard power source since they can no longer rely on power from the grid. While batteries are typically used in such applications, there are two major drawbacks: batteries (1) contain toxic materials and (2) need to be replaced. On the other hand, thermoelectric devices can harvest waste heat from their surrounding environment without a finite energy density, large components, and noise since they possess no moving parts [4, 6]. These characteristic traits have allowed thermoelectrics to be used in some maintenance-free applications for up to 20 years or more, even under extreme conditions with very little performance degradation [6]. With current performance and cost, the primary applications for thermoelectric devices are for space exploration and wireless devices in harsh and dangerous environments where the benefits outweigh the current cost and performance limitation. It is unlikely that thermoelectric devices will soon become cost-effective and efficient enough to compete with conventional large scale heat engines. However, if the material cost, manufacturing and integration technologies can be substantially improved, then thermoelectric devices could harvest the ~60% heat lost from conventional heat engines. With future improvements in the efficiency and cost, thermoelectrics can become commonly used energy harvesting devices, capable of powering a variety of applications such as implantable biomedical devices, remote sensors in hard to access locations, personal hand held electronics, and hybrid conventional heat engines.

**Figure 1-1.** Relative efficiency and possible applications of thermoelectric materials. (a) Power generation vs. efficiency plot illustrating how thermoelectric devices can become more efficient than conventional heat engines as the power consumption is scaled down to low power applications [4]. (b) Representative applications requiring a wide range of power consumptions that would benefit from thermoelectric devices [5].

## 1.2. Background on Thermoelectrics

#### 1.2.1. The Thermoelectric Theory

The thermoelectric effect is the physical phenomenon describing the relationship between a temperature gradient in a material and a corresponding electrical voltage. A thermoelectric device is a solid-state configuration of thermoelectric materials, which are often semiconductors, that utilize this phenomenon to convert a temperature gradient into a useful electrical voltage and current, or vice versa. The fundamental working principle is based around the movement of charge carriers within the thermoelectric materials: electrons in n-type materials and holes in p-type materials. In the presence of a temperature gradient, the respective charge carriers diffuse across the material from the warmer side to the cooler side. At the same time, an electrostatic repulsion potential

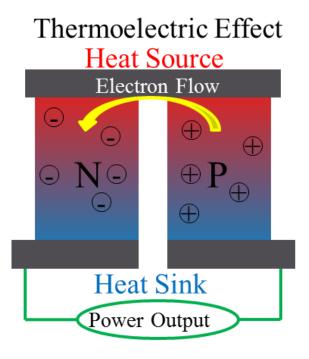

prevents a buildup of charge carriers at the cooler side. An equilibrium is reached between the diffusion potential and the electrostatic repulsion potential of the charge carriers, known as the thermoelectric or Seebeck effect [7]. In order to maximize the efficiency, thermoelectric materials need to preserve their temperature gradient by impeding thermal energy carriers while allowing the electrical charge carriers to flow with relative ease. Therefore, semiconductor based materials are most commonly used since metals have high thermal conductivities and low Seebeck coefficients while insulators restrict the flow of charge carriers due to their low electrical conductivity. A typical thermoelectric device consists of alternating p- and n-type semiconductors that are connected electrically in series and thermally in parallel (Figure 1-2). This configuration allows the holes and electrons to flow in opposite directions within their respective material, resulting in the flow of an electric current for power generation [6].

**Figure 1-2**. Schematic illustrating a representative thermoelectric device. A temperature gradient is applied across alternating p- and n-type semiconductors that are connected electrically in series and thermally in parallel.

The efficiency of a thermoelectric device is closely related to the semiconductor's material properties. In a non-degenerate semiconductor, phonons are the dominant thermal energy carrier. Ideally, a good thermoelectric device should behave as a "phonon glass", where phonons possess a very short mean free path such as found in glass and minimizing the thermal conductivity, but also as an "electron crystal" where electrons can travel over long distances unimpeded and maximizing the electrical conductivity [7]. The thermoelectric figure of merit, ZT, is often used to describe the conversion effectiveness:

$$zT = \frac{\alpha^2 \sigma T}{\kappa}$$

1-1

which is a dimensionless unit containing the Seebeck coefficient ( $\alpha$ ), mean absolute temperature (T), electrical conductivity ( $\sigma$ ), and thermal conductivity ( $\kappa$ ) [2, 5, 6, 8-12]. The thermoelectric figure of merit can be inserted into a modified Carnot efficiency equation to get the overall expected thermoelectric efficiency:

$$\eta = \frac{\Delta T}{T_h} \cdot \frac{\sqrt{1 + ZT} - 1}{\sqrt{1 + ZT} + T_c/T_h}$$

1-2

where the first term is simply the conventional Carnot efficiency and the second term is the correction factor based on the material's thermoelectric performance [7]. Current high performing thermoelectric materials have a zT close to 1, which needs to improve to greater than 3 to be competitive with conventional generators [7, 9, 13].

It is challenging to improve zT since the three intrinsic material properties that make up zT ( $\alpha$ ,  $\sigma$  and  $\kappa$ ) are closely coupled. Thus, as one parameter is tailored to improve zT another parameter counteracts the improvement [7]. For example, the Seebeck coefficient is the magnitude of the thermoelectric voltage under a temperature gradient. This effect is formed from the electric field that is generated when charge carriers are separated from their oppositely charged counterpart. Therefore, as the semiconductor carrier concentration (n) increases,  $\alpha$  decreases as show by:

$$\alpha = \frac{8\pi^2 k_B^2}{3eh^2} m^* T \left(\frac{\pi}{3n}\right)^{2/3}$$

1-3

where  $k_b$  is Boltzmann's constant, e is the elementary electron charge, h is Planck's constant, and  $m^*$  is the effective mass of the charge carrier [7]. At the same time, when the carrier concentration is increased,  $\sigma$  is also increased as shown by:

$$\sigma = ne\mu$$

1-4

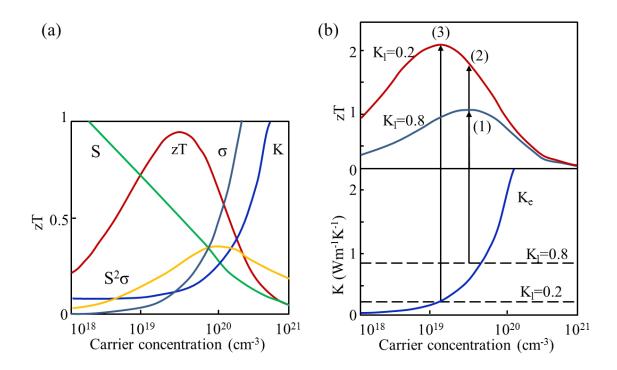

where  $\mu$  is the carrier mobility. Therefore, the power factor  $(\alpha^2\sigma)$  reaches a peak, typically in the heavily doped semiconductor range as show in Figure 1-3a [7]. In addition to  $\alpha$  being coupled to  $\sigma$  through the carrier concentration,  $\kappa$  is also coupled  $\sigma$  through the transport properties of the material. In any solid material,  $\kappa$  has two contributions:

$$\kappa = \kappa_e + \kappa_l \tag{1-5}$$

where  $\kappa_e$  is the transfer along with charge carriers and  $\kappa_l$  is transfer via phonons traveling along the lattice. The electron component  $\kappa_e$  is directly related to  $\sigma$  through the Wiedemann-Franz law:

$$\kappa_{e} = L\sigma T = ne\mu LT$$

1-6

where L is the Lorenz factor, typically  $2.44\cdot 10^{-8}\ J^2 K^{-2} C^{-2}$  for free electrons in bulk metals [14]. The primary contribution to the total thermal conductivity is  $\kappa_e$  in metals but  $\kappa_l$  in insulators and semiconductors. If  $\kappa_l$  can be reduced within a semiconductor without changing the electrical properties ( $\alpha$  and  $\kappa$ ) then zT would be increased (Figure 1-3b). However, increasing the ratio of  $\sigma/\kappa$  is a challenge since low  $\kappa_l$  materials are typically amorphous and insulating in nature, leading to low electrical properties compared to crystalline materials and therefore low zT values. Therefore, an efficient semiconductor

thermoelectric material possesses the electrical transport properties of a good crystalline material while being capable of effectively interfering with the phonon propagation to reduce the thermal conductivity [7].

**Figure 1-3.** (a) Representative illustration of the dependence of zT,  $\alpha$ ,  $\sigma$ , and  $\kappa$  over a range of carrier concentrations. Note that zT reaches a maximum value within a material due to the dependence between  $\alpha$ ,  $\sigma$ , and  $\kappa$ . (b) Illustration demonstrating that decreasing the lattice thermal conductivity can independently improve zT [7].

### 1.2.2. State-of-the-Art Thermoelectric Materials

Recent research on improving thermoelectric materials has focused on achieving three main goals. The first approach was sparked by Hicks and Dresselhaus in 1993 when

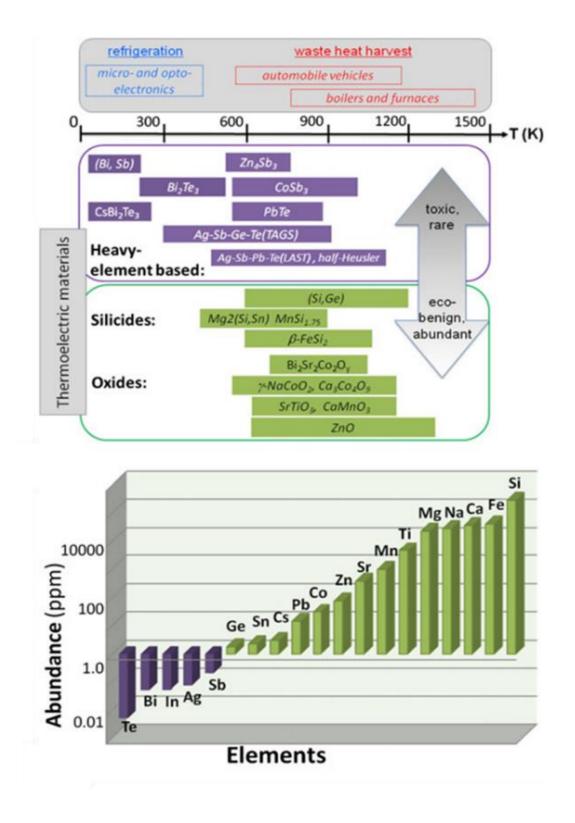

they suggested that nanostructured materials exhibit quantum confinement effects, which could provide a method to independently increase  $\alpha$  without decreasing  $\sigma$  [15]. The second approach is to increase the Seebeck Coefficient using phonon drag to transfer momentum from phonons to electrons [16]. This will slow down the phonon propagation while pushing the electrons forward. Unfortunately, this effect is only significant when the electron-phonon scattering is relatively high compared to the other phonon scattering mechanisms. Therefore, phonon drag only has a significant contributions when the electron-phonon scattering is dominate, which occurs around  $1/5 \Phi D$ , where  $\Phi D$  is the Debye temperature (~645°K for Si). Below 1/5 ΦD there are too few phonons for drag and above 1/5 ΦD the phonon-phonon scattering becomes the primary scattering mechanism. Low dimensional structures also have a relatively minor contribution from phonon drag since the low frequency phonons, which are the mainly responsible for phonon drag, tend to scatter on the low dimensional surfaces [16]. The third, and more sought after approach, is to increase  $\sigma/\kappa$  by typically reducing  $\kappa_l$  without reducing the electrical conductivity. The most common and successful approach to achieve an increase in  $\sigma/\kappa$  is with heavy-element based materials, in particular various alloys of Bi<sub>2</sub>Te<sub>3</sub> which have a zT close to 1 at room temperature [17]. In general, these materials create atomic disorder in the lattice by inserting point defects such as heavy elements. These effectively act as dampers to suppress the phonon propagation while still maintaining the crystalline structure to preserve the electrical conductivity. While somewhat successfully, this approach has major drawbacks to scalability: the heavy element based materials tend to be rare earth materials that are rather toxic, which makes the technology expensive, hard to mass produce, undesirable and detrimental to our natural resources (Figure 1-4).

An alternative approach is to engineer thermoelectric materials that are comprised of cheap, abundant, and environmentally friendly materials that can be mass produced despite having low zT values. These materials include oxides, silicides and polymers [17, 18]. While these methods are promising for their cost, scalability, and lack of toxicity, their zT values are far from practical due to their low carrier mobility or high lattice thermal conductivities [12]. Figure 1-4 shows another group of materials, Si/Ge, that can be used for thermoelectrics. Si, in particular, is always a great material to invest a technology on since it is the second most abundant element on earth after oxygen. Also years of knowledge and technology have been devoted to processing devices based around Si, making it very well characterized. However, crystalline Si in bulk form is a poor thermoelectric due to the high  $\kappa_1$  and low  $\alpha$ , resulting in a zT around 0.01 [19].

**Figure 1-4.** Summary of promising thermoelectric materials and their relative element abundance. Heavy element based thermoelectric materials are currently the best

performing thermoelectric materials but suffer from cost, limitations to scalability, and toxicity, while silicides and oxides are cheap, abundant, and environmentally friendly but suffer from poor performance. Bulk Si, although not very efficient, has the benefits of being very abundant with years of knowledge and technology invested into modifying Si for desirable application. Reprinted from [17].

#### 1.2.3. Potential of Nanostructured Silicon

Nanostructuring of semiconductors into thin films, wires, and quantum wells has been used since the 1960s to achieve unique material properties not possible in bulk form [11]. Nanostructured silicon, in particular, has the potential to reduce  $\kappa_l$  without reducing  $\alpha^2\sigma$  due the relatively long average bulk Si phonon mean free path ( $\lambda_{bulk\_Si} = \sim 300$  nm) compared to the average electron mean free path ( $\sim 10$  nm). The large difference in these mean free paths allow Si nanostructures to be fabricated with critical internal and/or external dimensions larger than the average electron mean free path but smaller than the average phonon mean free path ( $\lambda$ ). Under these conditions, the nanostructured dimensions will increase phonon scattering at the surfaces resulting in a reduced average phonon mean free path ( $\lambda_{nano\_Si}$ ) as shown by Matthiessen's rule:

$$\frac{1}{\lambda_{\text{nano_Si}}} = \frac{1}{\lambda_{\text{bulk_Si}}} + \frac{1}{d}$$

where d is the critical nanoscale dimension. The thermal conductivity will be reduced proportionally to the reduction in  $\lambda$  through the following equation:

$$\kappa = \frac{1}{3}C\nu\lambda \tag{1-8}$$

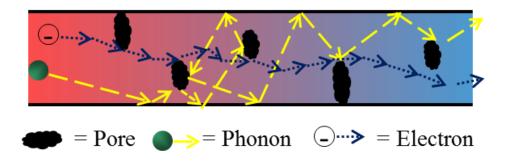

where C is the phonon specific heat capacity and  $\nu$  is the phonon group velocity. An illustration demonstrating enhanced phonon scattering within nanostructured Si is shown in Figure 1-5.

**Figure 1-5.** Schematic illustrating the electron and phonon transport in nanostructured Si. Notice the electron can move relatively easily through the structure without being affected while the phonon scatters at various internal and external boundaries, leading to a reduced average phonon mean free path.

Si-Ge superlattices were one of the first nanostructured Si materials developed with the goal of reducing  $\kappa_l$  for thermoelectric applications. These structures have layers ranging from 20 to a few hundred angstroms thick and estimated  $\kappa_l$  around the equivalent alloy composition [20, 21]. While the superlattice structures hold promise to reduce  $\kappa_l$ , the time-consuming and expensive molecular-beam-epitaxy process makes it unlikely to be cost-effective for scalable thermoelectric devices. On the other hand, porous Si is a cost-effective nanostructured Si material capable of reducing  $\kappa_l$  up to three orders of magnitude compared to bulk Si [22-25]. Computational results of ordered porous Si has

been shown to have relatively little degradation in the electrical properties making it promising for thermoelectrics [26-28]. However, typical porous Si has random, disordered pore formation with deteriorated electrical properties [25, 29-32]. Researchers have expanded the porous Si concept by patterning two-dimensional periodic larger microporous thin films to alleviate the electrical deterioration concern [33-35]. These films have shown an increase up to 50 times in performance with a zT of 0.4 [35]. While promising, these two-dimensional structures are formed using expensive silicon-on-insulator wafers and would be a challenge to scale up for three-dimensional configurations.

Si nanowires have recently received substantial interest as building blocks for thermoelectric devices with material properties that could closely resemble an ideal "phonon glass, electric crystal" material. Experimental measurements have demonstrated that a single Si nanowire could have as much as a 100x decrease in thermal conductivity compared to the bulk Si with the phonon contribution reduced close to the amorphous limit [19, 36, 37]. In particular Si nanowires with rough surfaces have shown to have a more substantial thermal conductivity reduction compared to smooth Si nanowires fabricated with similar diameters [19, 38-42]. However, the observation of reduced thermal conductivity has been limited to a single nanowire, so this theory needs to be tested over bulk nanostructured nanowires to evaluate the actual performance of a practical device.

## 1.3. Opportunities and Challenges

## 1.3.1. Vertical Si Nanowire Array Based Thermoelectric Devices

Preliminary research has demonstrated that nanostructured Si, particularly nanowires, are a promising low cost, non-toxic material for future thermoelectric materials. It is believed that Si nanowires with rough surfaces are capable of achieving a 100x reduction in the thermal conductivity, which would increase zT to around 1. While this current projected efficiency is on par with the best performing heavy element based thermoelectric materials, the drastic reduction in cost and environmental impact would make Si based thermoelectric devices applicable for large range of everyday applications. However, in order to achieve the substantial improvement in zT, several fundamental and fabrication challenges need to be addressed. First, the fundamental understanding of the Si nanowire fabrication methods needs to be improved to accurately and repeatedly fabricate and characterize the nanoscale features within the Si nanowires. Second, highly dense vertical Si nanowire arrays need to be fabricated to enable array-scale characterization. Third, the general trends of the Si nanowire features need to be investigated to determine the impact on the thermal conductivity. Fourth, fabrication methods need to be developed to remove the residual and performance-limiting Si substrate from the Si nanowire arrays without disturbing the array morphology. Finally, Si nanowires arrays need to be directly integrated between metal electrodes for complete thermoelectric device assembly as well as electrical characterization while still maintaining their vertically aligned morphology and uniform length.

#### 1.3.2. Additional Vertical Si Nanowire Arrays Based Applications

In addition to reducing thermal conductivity, vertical SiNW arrays possess unique material properties opening up new opportunities as potential building blocks for numerous other applications including sensors [43-50], solar cells [51-59] and Li-ion batteries [60-66]. For example, ultra-sensitive chemical and biological sensors are possible due to the high surface area to volume ratios and the reproducible electronic properties allow Si nanowires to be uniquely sensitivity to surface analyte adsorption. Conventionally Si nanowire based sensors are fabricated by depositing nanowires suspended in a solution on a planar substrate that are subsequently connected between metal source and drain electrodes [44, 47]. While promising, commercialization of the planar Si nanowire configuration has been limited due to slow processing times, unreliable results from irreproducible nanowire dimensions and surface chemistry, size dependent noise sources, and substrate effects [49]. The ability to overcome the challenge of separating vertical Si nanowire arrays from the Si substrate is necessary to enable metal electrodes to contact both sides of the array directly, minimizing the above problems and exhibiting high sensitivity capable of detecting as little as a few parts per billion [49, 50].

Vertical Si nanowire-based solar cells are another promising application, leveraging the Si nanowire capabilities to enhance light absorption and decouple the direction of light absorption from carrier extraction, making these arrays promising for low-cost, efficient solar cells. The highly aligned Si nanowire array structure is capable of trapping light, allowing the photons more opportunity to be absorbed and therefore requiring less

silicon [54]. In typical planar silicon, a photon is absorbed in the silicon, which can be a couple of hundred micrometers into the Si to form an electron/hole pair. The minority carriers then have to travel this same distance back towards the p-n junction, increasing the chance of recombination and thus requiring highly pure Si. Radial junction solar cells, are capable of decoupling the direction of light absorption from carrier extraction, so when a photon is absorbed in Si, the minority carriers only have to travel a maximum distance equal to the radius of the wire, reducing the need for highly pure silicon [53, 59]. The ability to separate Si nanowire from a reusable substrate can drastically reduce the quantity and quality of silicon required for a low-cost, efficient solar cell.

A third additional example demonstrating the potential of vertical Si nanowire arrays is the anode of Li-ion batteries. Conventional Li-ion batteries use carbon based materials for the anode material, which has a theoretical storage capacity of 372 mAh/g [62]. Silicon, on the other hand, has a much larger theoretical storage capacity of ~4200 mAh/g, resulting in a more than six times increase in the overall storage capacity [62]. One issue that arises during operation is the large volume expansion of Si, up to 400%, when Li ions are inserted into Si. This results in the pulverization of Si which can damage the contact to the current collection and decrease the overall charge storage capacity over time [62-64]. Vertical silicon nanowires array, due to their small dimensions are capable of withstanding the high strain formed during the lithiation process. This allows Si nanowires to be used as an anode material capable of being used over many charge and discharge cycles without a decrease in performance. The vertical Si nanowire arrays will need to overcome the challenge of removing the Si nanowire

array from the bulk Si substrate in order to be directly connected to a current collector, bypassing any bulk Si that can lead to pulverization.

## 1.4. Scope and Organization of Thesis

The main body of this thesis contains 5 chapters. The first main chapter (Chapter 2) examines a range of methods that are used to form a wide variety of nanostructured Si. The next chapter measures the thermal conductivity of the nanostructured Si nanowire arrays. The last three body chapters tackle the challenge of transferring large area, high dense Si nanowire arrays to non Si substrates.

- Chapter 2 describes a variety of top-down Si nanostructuring methods that range from porous Si to non-porous Si nanowire arrays and everything in between.

- Chapter 3 develops a fabrication method capable of using an optical method to

measure the thermal conductivity of a Si nanowire array film. The Si nanowire

fabrication method is varied to control both the internal and external phonon

scattering sites with a range of porosity and Si nanowire diameter.

- Chapter 4 develops a method to chemically form a horizontal crack through a SiNW array, effectively weakening the adhesion between the array and bulk substrate. The array can subsequently be transferred from the Si substrate to any material, including flexible, transparent or conducting substrates.

- Chapter 5 utilizes the transfer method in Chapter 4 to fabricate Si nanowire array electronic devices. The properties of the Si nanowires are varied to achieve the electrical performance of both highly porous and marginally-porous Si nanowires.

• Chapter 6 expands on the methods in Chapter 4 and 5 to develop a new more universal method that is capable of transferring any Si nanowire array to arbitrary substrates for device integration regardless of the Si nanowire array fabrication method.

# **Chapter 2. Experimental Nanostructured Silicon**

## **Fabrication Methods**

Nanostructuring of silicon (Si) has received increasing substantial interest over the past few decades due to its ability to possess unique material properties that are not possible in bulk form [67, 68]. The fabrication of these Si nanostructures is often separated into two categories; bottom-up and top-down. Since the early 1990's, bottomup techniques have been the more favorable single crystalline Si nanostructuring method. In particular the vapor-liquid-solid (VLS) growth method has received substantial attention for the synthesis of Si nanowires (SiNWs). VLS SiNWs form in a chemical vapor deposition (CVD) chamber through the absorption of a Si based gas precursor at a liquid catalytic alloy, typical gold (Au), at a temperature higher than the eutectic point (300-400 °C) [69-71]. The liquid catalyst serves as the preferred decomposition site of the Si atoms from the gas precursor until the catalyst becomes supersaturated with Si, at which point Si crystallizes beneath the catalyst, forming SiNWs. While the VLS method is a well-developed SiNW synthesis method, it suffers from a few limitations and drawbacks. First, the CVD setup and growth process is rather expensive and is typically limited to small growth areas due to the chamber size. Second, the SiNW density is relatively low due to the challenge of preventing the close-packed catalyst particles from merging at the growth temperature [72]. Third, achieving a high degree of vertical alignment is often a challenge. Fourth, the SiNWs can be doped through a variety of methods, including with the metal catalyst or the addition of a dopant gas; however, accurately predicting the resulting dopant level is very challenging [68]. Finally, during

the high temperature growth process, the metal catalyst diffuses into the SiNWs forming crystallographic defects and trap sites that reduce the minority carrier lifetimes [68, 73].

Top-down etching methods start with a bulk Si wafer and remove materials rather than add material. These offer the potential to alleviate some of the limitations and drawbacks associated with the bottom-up synthesis of Si nanostructures. For example, since the resulting SiNWs are etched from a bulk wafer, the doping concentration is based on the original wafer and the high temperature growth conditions are eliminated, removing the crystallographic defect sites. Furthermore, precise scalable patterning methods can be used to form highly aligned, dense Si nanostructures over a large area, making the top-down technique a very promising method. This chapter will go over a range of top-down etching methods beginning with the basics of forming porous Si and expanding to highly aligned SiNW fabrication and modification methods.

## 2.1. Porous Silicon Formation: Etching Chemistry and Theory

Porous Si was discovered by accident in the mid-1950s, while attempting to develop an electrochemical method to polish the surface of Si and germanium (Ge) [74]. Instead of polishing the Si as expected to form a reflective surface, a brittle dark film was found that contained porous holes propagating primarily in the <100> direction through the Si wafer. Although this was recorded in a technical report at Bell Labs, it did not receive substantial interest until the early 1990s when it was determined that porous Si can emit visible light [75, 76]. A plethora of work focused on creating porous Si based

optoelectronics was reported during the mid-1990s until it slowly calmed down due to disappointing electroluminescence efficiency, and poor chemical and structural stability [77]. Since then, the fundamental understanding of porous Si has been improved and is currently being used in a wide range of applications from drug delivery systems, optoelectronics, sacrificial materials, energy storage and harvesting devices [26, 77-81].

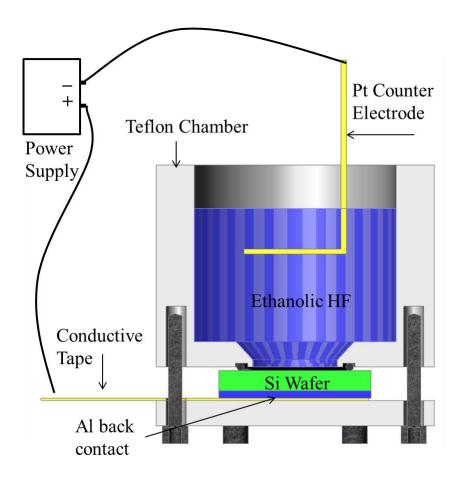

#### 2.1.1. Anodization

While Si is thermodynamically unstable in air and water, forming a native oxide layer, in the presence of hydrofluoric acid (HF) the oxide is rapidly removed leaving the surface hydrogen terminated (Si-H) [82]. The Si-H bonds passivate the surface preventing further oxidation in aqueous HF without the presence of strong oxidation agents. A common and controlled method to promote the continued oxidation of Si is through anodizing the Si in an HF solution. A typical anodization cell, shown in Figure 2-1, is composed of a Teflon chamber with a circular opening where a clamped piece of Si wafer is exposed to the solution. A power supply is connected to the cell, supplying a constant current to flow through the Si wafer with a metal back contact, acting as an anode, to a platinum (Pt) counter electrode submerged in the HF electrolyte solution, allowing an electrochemical reaction to form at the interface of the Si and solution (see Appendix A for more details). Although porous Si forms in HF solutions diluted with deionized water, the hydrophobic properties of the hydrogen terminated surface hinder the ability of the solution to infiltrate the pores and therefore induces lateral and in-depth inhomogeneity [79]. Thus, ethanolic solutions are commonly used to increase the wettability on the porous Si surface, allowing the solution to infiltrate the pores [77].

Figure 2-1. Cross-sectional schematic of an anodization cell used to form porous Si.

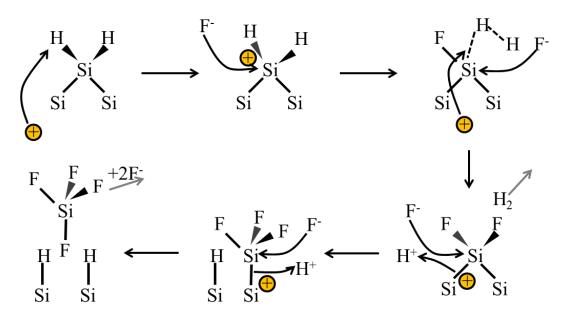

The dissolution of Si is obtained by supplying either an anodic current or potential; however, supplying a constant current allows for superior control and reproducibility [83]. The power source supplies holes to the Si valence band, oxidizing the Si surface. The holes are driven to the surface by diffusion from the electric field generated within the wafer. At the Si surface, holes break apart the Si-H bonds causing competition between the formation of Si-H, Si-O and Si-F bonds [77]. The Si-F bond has the highest electronegativity, making it the favorable bond with Si-O being the second most likely. The high electronegativity makes the Si-F bond highly polarized, so as soon

a fluoride ion attaches to a Si atom it becomes the preferred atom for the subsequent holes to attach to, leading to the rapid dissolution of the Si atom into water as soluble  $SiF_6^{2-}$  as shown in Figure 2-2 [77].

Overall Reaction at Silicon Surface:  $Si + 6F^- + 2H^+ + 4h^+ \rightarrow SiF_6^{2-} + H_2$

**Figure 2-2.** Reaction model for the anodic dissolution of Si in the presence of hydrofluoric acid [77].

The preferred crystal plane direction for the removal of Si in HF is related to the energy associated with cleaving the Si back-bonds [84]. The effected number density of back-bonds increases relative to the crystal plane in the order of (100) < (110) < (111); therefore, the pores typically propagate along the <100> direction [85]. However, the pore morphology, size and overall porosity greatly depend on the wafer, solution, and

applied conditions during the porous Si formation process. Varying the wafer type and doping level will affect the pore formation mechanism, which in turn affects the size and directionality of the pores [86]. For example micropores (pore width  $\leq 2$  nm) are often formed in low and moderately doped p-type Si with the most uniform porosity. Mesopores (2 nm < pore width  $\leq 50$  nm) are often formed with highly doped p- and n-type wafers with pores perpendicular to the wafer surface due to the enhanced electric field driving the holes towards the base of the pore. Macropores (pore width > 50 nm) are often formed in low doped n-type wafers with pores forming perpendicular to the surface due to the space charge region depleting the holes around the pore [77, 83]. The pore size and morphology can also be tuned through varying the solution or conditions. In general, increasing the current density, increasing the temperature or decreasing the HF concentration has a similar affect, leading to an increase in the pore size and porosity [77, 78, 84, 86-88].

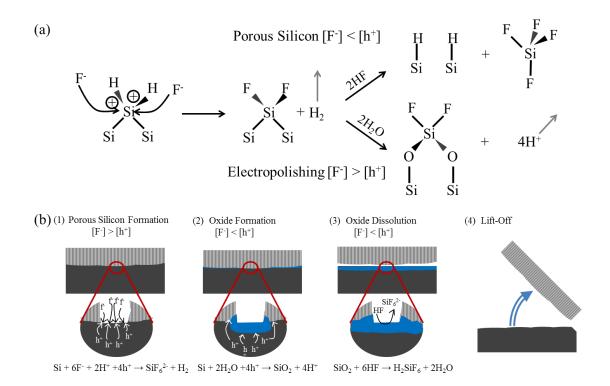

#### 2.1.2. Electropolishing

As mentioned earlier, the Uhlirs discovered porous Si formed under certain conditions while trying to develop an electrochemical method to polish Si and Ge [74]. If the porous Si conditions are modified in a particular way, electropolishing occurs which is very beneficial for releasing thin porous layers from bulk Si wafers [89]. The key condition required for electropolishing is the rate the current injects holes into the Si surface has to exceed the rate that fluorine ions can be transports to the pore tip [77, 90-93]. Under this condition, the fluorine ions cannot keep up with the rate the holes are injected into Si valence band, which leads to the formation of Si-O bonds as shown in

Figure 2-3a. After a brief amount of time, a continuous oxide layer will spread underneath the entire porous layer which will be followed by the HF attacking the continuous oxide layer, resulting in the liftoff of the original porous film (Figure 2-3b).

**Figure 2-3.** (a) Reaction model pathways of the anodic dissolution of Si during porous Si formation and electropolishing. (b) Schematic demonstrating the lift-off of a porous Si film: (1) A porous Si layer is formed, (2) the hole inject rate exceeds the fluorine mass transport rate as an oxide layer starts to form, (3) hydrofluoric acid attacks the now continuous oxide layer, (4) the oxide layer is removed, allowing the free-standing porous Si film to be lifted off from the Si substrate [77].

There are two primary methods to ensure that the rate of hole injection into the valence band exceeds the mass transport rate of fluorine ions to the Si/solution interface

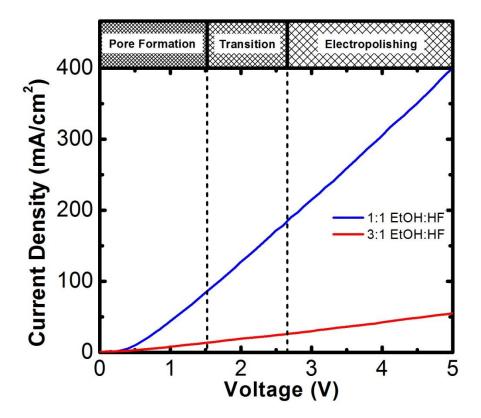

as shown in Figure 2-4. The first method is to substantially increase the current density while keeping the solution constant (blue line). The second method is to reduce the HF solution concentration which in turn reduces the number of available fluorine ions (blue to red line). Both of these or a combination of these methods work; however, it has been reported that a higher surface quality is obtained when the HF concentration is reduced rather than increasing the current density (see appendix A for additional details) [92]. A transition region occurs between the pore formation and electropolishing regions. In this region the number of holes injected into the valence band and fluorine ion concentration are approximately equal so oxygen and fluorine ions compete for control over the Si surface bonds [84]. The resulting surface is porous in nature; however, the pore sizes significantly increase as the potential approaches the electropolishing potential [84, 86, 87]. It is important to note that porous Si is very fragile, so a delicate drying method, such as critical point drying, is often required to preserve the porous Si especially after a lift-off process.

**Figure 2-4.** Exemplary current density vs. voltage curve for a Si wafer with a p-type boron dopant concentration of 10<sup>16</sup> cm<sup>-3</sup> in a 1:1 and a 3:1 ethanol:hydrofluoric acid solution. The Si dissolution goes from porous Si formation to electropolishing with a transition region in the middle as the voltage potential is increased by either increasing the current or decreasing the hydrofluoric acid concentration.

#### 2.1.3. Stain Etching

Stain etching is a less common but easier alternative method to prepare thin porous Si layers. This method produces porous Si films on crystalline Si wafers with a red or brownish color, hence the name "stain etching" [94]. Instead of anodically oxidizing the Si with a constant current or potential, an oxidizing agent is added to the

hydrofluoric acid solution, typically nitric acid (NHO<sub>3</sub>). The nitric acid is reduce to nitric oxide (NO) by equation (2-1 below, which serves as the hole injector to oxidize the Si valence band [95].

$$HNO_3 + 3H^+ \rightarrow NO + 2H_2O + 3h^+$$

(2-1)

It has been reported that the hole injection into the Si is actually catalyzed by NHO<sub>2</sub> rather than NHO<sub>3</sub>, so that there is a necessary incubation period required for the concentrated nitric acid to react before the initiation of pore formation [96]. The incubation time can vary from a few seconds to multiple minutes and is also linked to the Si wafer doping type and density [97]. Although stain etching is a simple and easy method, its nonuniformity, unreliable reproducibility, and slow induction period limit its use as a porous Si formation method.

## 2.2. Top-Down Non-porous Silicon Wire Formation

#### 2.2.1. Deep Reactive Ion Etching

Vertically aligned non-porous Si wires are fabricated using the conventional Deep Reactive Ion Etching (DRIE) process, often referred to as the Bosch Process. Prior to DRIE, a Si wafer was cleaned in a 3:1 (v/v) H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub> for 10 minutes, followed by a 10 minute 2% HF dip. The Si wires are patterned with photoresist or a silica sphere masking layer (see Appendix B for more details). The Si wire arrays are formed by DRIE with cycles of 6 second etching with 130 sccm of SF<sub>6</sub> and 5 second passivation with 120 sccm of C<sub>4</sub>F<sub>8</sub> in a 600W plasma. The etch time will vary depending on the exposed Si area and the desired Si wire length. The Si wires are fabricated approximately 10-20 μm

in length with diameters ranging from a few microns to approximately 300 nm depending on the patterning method. The Si wire diameter is limited to above 300 nm due to the on/off etch/passivation steps forming scalloped sidewalls along the length of the wire which is too severe in Si wires below 300 nm in diameter.

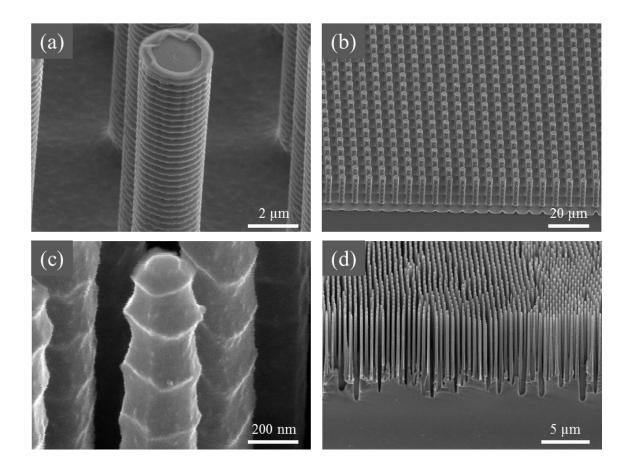

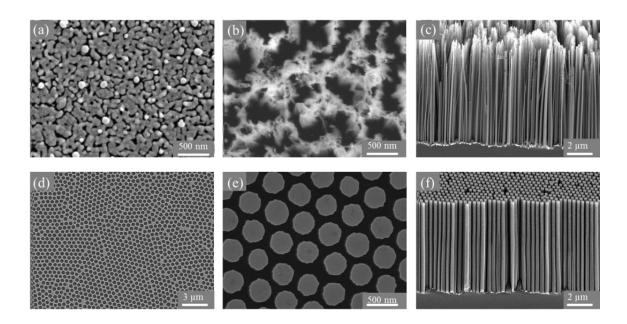

Si microwires, as shown in Figure 2-5a,b, are patterned using conventional photolithography. The DRIE masking layer consists of a 1 µm thick photoresist layer that is exposed and developed, leaving behind an array with 3 µm diameter circular features at a 7 µm pitch. SiNWs, as shown in Figure 2-5c,d, are patterned using nanosphere lithography with silica spheres, which is described in more detail in the following sections. In this case, it is important to note that the final SiNW diameter is smaller than the original sphere size and slightly tapered along the length of the wire [53]. This is due to the silica spheres being etched despite the 100:1 selectivity of silica to Si which therefore limits the possible SiNW aspect ratio.

**Figure 2-5.** SEM images of (a,c) close-up and (b,d) zoomed-out Si (a,b) microwire and (c,d) nanowire arrays formed by the DRIE process.

#### 2.2.2. Nanosphere Lithography

Nanosphere lithography is a simple, inexpensive, high throughput, self-assembly method to pattern periodic uniform nanoscale features [98-103]. It typically consists of the formation of a hexagonal close-packed monolayer of nanospheres, although recent research has investigated the benefits of creating double or multiple layers of spheres for the formation of unique patterns or inverse opal structures [98, 100, 103-108]. In order to form a masking layer for individual SiNWs, the close-packed monolayer of spheres needs

to become non-close-packed. While there are large area methods to manipulate the spheres to be non-close-packed such as deformable soft lithography [109-111], the most reliable technique involves dry etching the spheres to reduce their size. Dry etching of the spheres allows precise control over the SiNW diameter and spacing [112].

Nanosphere lithography can be performed using a range of sphere materials and deposition methods. Dip coating, drop casting and spin coating are some of the methods that are considered as quick and cost effective methods to deposit a monolayer of spheres; however, the as-formed monolayers suffered from forming close-packed domains with multiple defective areas of voids or sections of multilayers distributed over the sample area. The Langmuir-Blodgett (LB) method, while more labor intensive, provides an alternative method of forming a high quality monolayer over a large area, which is crucial for fabricating reliable and consistent large-area vertical SiNW array devices. The LB method is achieved by first filling an LB trough (Figure 2-6) with DI water, followed by the slow injection of silica spheres through a syringe. The barrier walls are then slowly compressed while the surface pressure is carefully monitored using a Wilhelmy plate. A quick spike in the surface pressure occurs when barriers are compressed enough to form a close-packed monolayer of spheres on the water surface. A substrate is then dipped into the DI water and slowly pulled out at a constant rate allowing the spheres to be transferred from the water surface to the substrate.

**Figure 2-6.** Schematic of the Langmuir Blodgett Trough used to deposit a monolayer of silica spheres for nanosphere lithography.

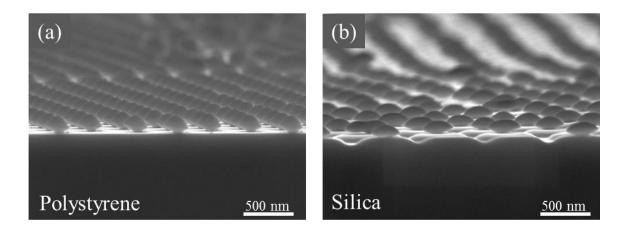

Polystyrene and silica spheres are the most common materials used for nanosphere lithography. Polystyrene spheres have the benefit over silica spheres of isotropic sphere reduction in O<sub>2</sub> plasma which allows greater sphere spacing to diameter ratios, smaller SiNW diameters, and a sphere etching method that does not affect the Si substrate (Figure 2-7) [113]. However, silica spheres offer the advantage of in-lab sphere synthesis and controlled functionalization capable of preparing spheres for use in a LB trough and therefore are the preferred sphere material used in the majority of the work in this thesis [72].

**Figure 2-7.** SEM images of (a) 490 nm polystyrene spheres etched in O<sub>2</sub> plasma (3 minutes, 20 sccm O<sub>2</sub>, 50 mtorr, 100 W) and (b) 650 nm silica spheres etched in a fluorine-based plasma (7 minutes, 6 sccm O<sub>2</sub>, 85 sccm CHF<sub>3</sub>, 40 mtorr, chamber power of 1600 W)

#### 2.2.3. Silica Sphere Creation and Functionalization

Although silica spheres can be readily purchased, I synthesized our own nanospheres in lab using a modified Stöber synthesis [114]. This sol-gel synthesis is based on the reaction of tetraethoxysilane (TEOS) with water in the presence of an ammonia catalyst to produce silica as show in equation 2-2 [115-117].

$$Si(OC_2H_5)_4 + 2(H_2O) \xrightarrow{NH_3} SiO_2 + 4(C_2H_5OH)$$

(2-2)

The resulting silica particle diameters are a function of a number of factors, including solution pH, temperature, mixing conditions, reaction time, reagent and catalyst concentration [114-116, 118]. The following equation can be used as a rough

approximation to determine the silica sphere size, d, in nanometers as a function of the reagent concentration in mol/L [115, 119].

$$d = A[H_2O]^2 exp(-B[H_2O]^{1/2})$$

(2-3)

where

$$A = [TEOS]^{1/2}(82 - 151[NH_3] + 1200[NH_3]^2 - 366[NH_3]^3)$$

$$B = 1.05 + 0.523[NH_3] - 0.128[NH_3]^2$$

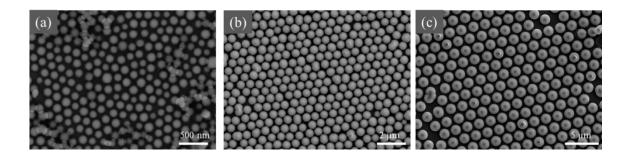

Silica spheres with diameters ranging from roughly 75 nm up to 700 nm can be fabricated using this method while spheres, as large as 1 µm can be purchased from online suppliers (Figure 2-8). A general fabrication recipe used to synthesize 650 nm spheres can be found in appendix C. Silica spheres with diameters less than 150 nm are unable to be cleaned through solvent exchange due to limitations in separating the silica sphere from the solvent during centrifuge cycles.

**Figure 2-8.** SEM images of a monolayer of silica sphere with diameters of (a) 175 nm, (b) 650 nm and (c) 2 μm.

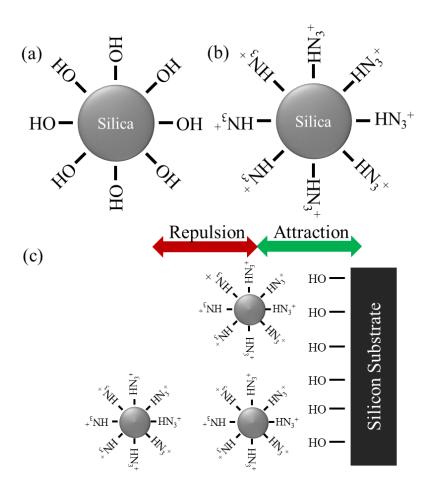

A successful deposition of a monolayer of spheres via Langmuir Blodgett assembly requires the silica spheres to have amphiphilic properties with a hydrophilic and hydrophobic balance. The surface of the silica spheres can be modified from a hydroxyl group to amino group using a surfactant, such as 3-aminopropyltriethoxysilane (APTES). The positively charged amino group prevents aggregation of the silica spheres while also supplying an attractive force to a hydroxyl terminated Si wafer, as shown in Figure 2-9. Detailed steps on the functionalization of silica spheres with APTES can be found in appendix D.

**Figure 2-9.** Schematic of (a) as formed hydroxyl terminated silica spheres, (b) amino group terminated silica spheres after functionalization in APTES and (c) attraction and

repulsion of silica spheres to a hydroxyl terminated substrate and functionalized silica spheres, respectively.

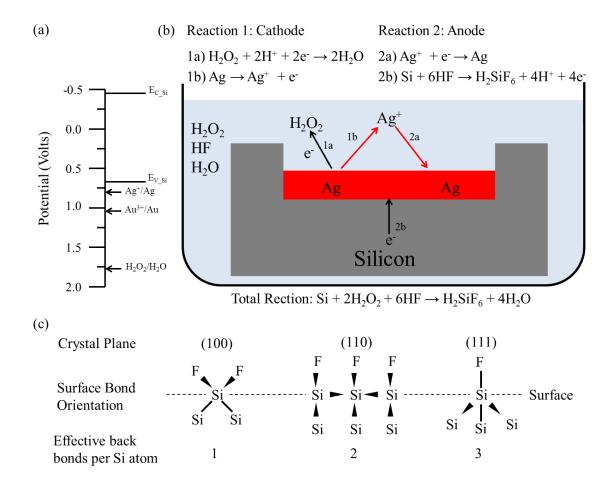

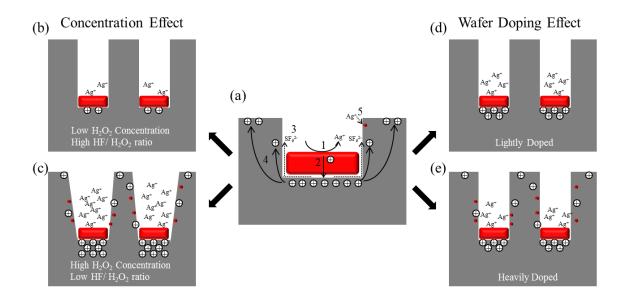

## 2.3. Metal-Assisted Chemical Etching

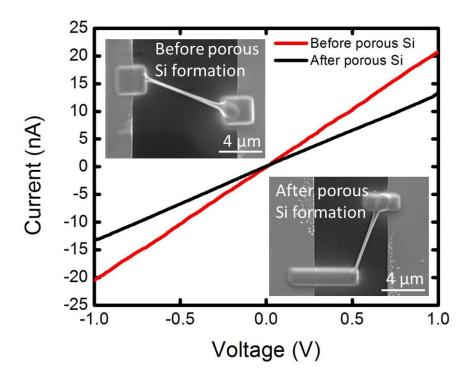

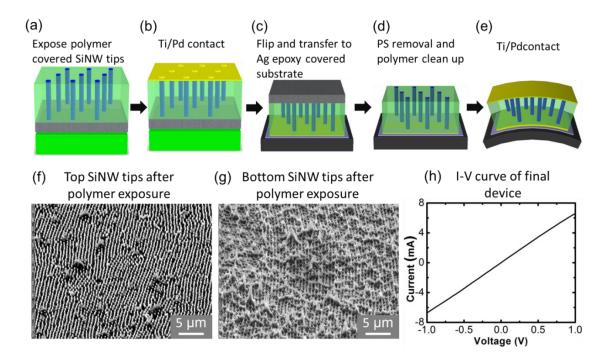

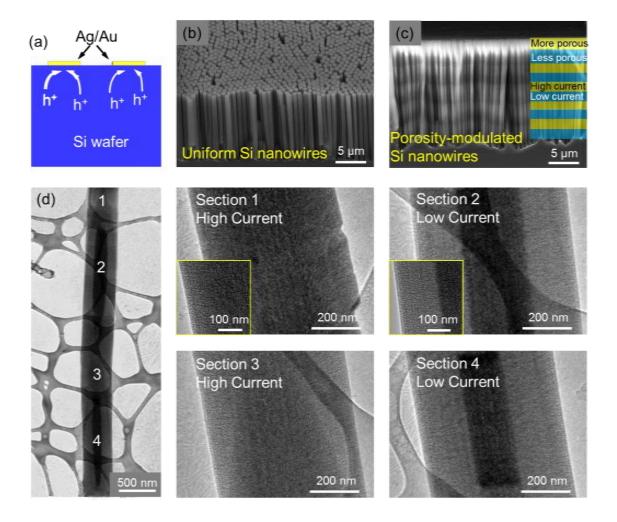

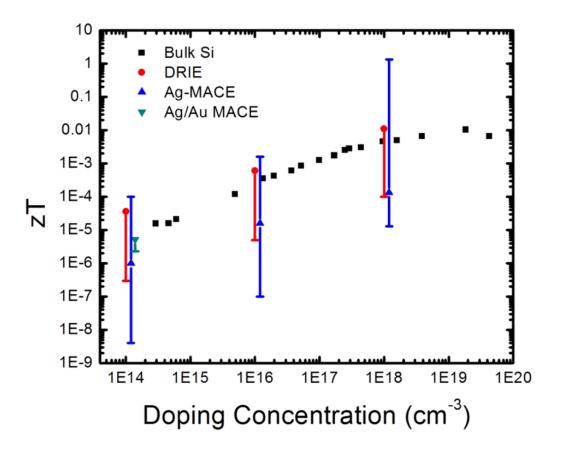

Metal-Assisted Chemical Etching (MACE) is relative new and appealing method to form high aspect ratio SiNW arrays for several reasons. First, the etching mechanism is very similar to that of porous Si but with an etching direction selectivity that surpasses that of DRIE to form SiNWs with high aspect ratios. Second, MACE is a simple, fast and low cost method that can be done in a lab without expensive or time consuming Third, the etching mechanism forms SiNW arrays regardless of the wafer doping type or concentration. Fourth, the SiNWs can be patterned to vary their shape, size, area and density. There is no clear limitation of the achievable SiNW diameter; however, straight SiNWs can be formed with diameters ranging a low as 5 nm up to 1 um [73]. Fifth, the etching condition and catalyst can be tuned to produce SiNWs that range from almost non-porous to highly porous. Electochemical etching of Si occurs anisotropically along the <100> direction and therefore a (100) substrate is preferred to form vertically aligned SiNW. However, researchers have developed methods to form vertically aligned SiNWs on non-(100) substrates or form slanted, zig-zagged, or spiral shaped NWs or pores [120-122]. The above reasons are why MACE has become a very promising SiNW fabrication method in the past decade in efforts to take a step forward in realizing the practicality of SiNW arrays in functional devices.