# THERMAL CONDUCTION PHENOMENA IN NANOSTRUCTURED SEMICONDUCTOR DEVICES AND MATERIALS

### A DISSERTATION

# SUBMITTED TO THE DEPARTMENT OF MECHANICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

Zijian Li

August 2012

# © 2012 by Zijian Li. All Rights Reserved.

Re-distributed by Stanford University under license with the author.

This work is licensed under a Creative Commons Attribution-Noncommercial 3.0 United States License. http://creativecommons.org/licenses/by-nc/3.0/us/

This dissertation is online at: http://purl.stanford.edu/yj710pk3626

| I certify | that I have | read this  | s dissertation | and that, | in my   | opinion,   | it is fully | adequate |

|-----------|-------------|------------|----------------|-----------|---------|------------|-------------|----------|

| in scope  | and quality | y as a dis | sertation for  | the degre | e of Do | octor of l | Philosoph   | ıy.      |

## Kenneth Goodson, Primary Adviser

| I certify | that I have | read this | dissertation | and that, | in my o | opinion,   | it is fully | adequate |

|-----------|-------------|-----------|--------------|-----------|---------|------------|-------------|----------|

| in scope  | and quality | as a diss | ertation for | the degre | e of Do | octor of I | Philosoph   | y.       |

Mehdi Asheghi

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

**Philip Wong**

Approved for the Stanford University Committee on Graduate Studies.

Patricia J. Gumport, Vice Provost Graduate Education

This signature page was generated electronically upon submission of this dissertation in electronic format. An original signed hard copy of the signature page is on file in University Archives.

# **Abstract**

Thermal phenomena have become very important in a variety of nanostructured semiconductor devices and materials. The reduced dimensions and large interface densities lead to complex thermal phenomena which do not occur in bulk materials and larger devices. Successful designs of high-performance semiconductor devices, including phase change memory (PCM) and high electron mobility transistors (HEMT), rely on the accurate thermal characterization of thin film materials and improved understanding of nanoscale energy transport physics. This thesis addresses nanoscale thermal transport problems relevant for three promising electronics technologies.

The first part of this work investigates thermal conduction phenomena in phase change memory. A combination of frequency-domain electrical thermometry and suspended microstructure design are used to measure the in- and out-of-plane thermal conductivities of thin-film  $Ge_2Sb_2Te_5$  in the amorphous and crystalline phases. The preferential grain orientation and mixed phase distribution lead to a reduced in-plane thermal conductivity that is 60% - 80% of the out-of-plane value. Anisotropic heat conduction benefits PCM devices by reducing the programming current and mitigating the thermal disturbance to adjacent cells. A fully coupled electrothermal simulation unveils the detailed transient phase distribution during a programming operation, enabling more efficient structural designs for multilevel memory operation.

This research extends the thermal characterization and modeling techniques to diamond-based high electron mobility transistors. The high thermal conductivity of the diamond provides superior thermal performance and allows for up to 10x higher power density. Nanoheaters down to 50 nm wide are patterned by electron-beam lithography in order to measure the thermal resistance experienced by the single transistor channel, the multi-gate configuration, and the device package. The thermal resistance data reveals the critical role of thermal interface between the GaN device

layer and the diamond substrate. This work established a criterion for the diamond technology to be viable in HEMT applications. Specifically, the thermal interface resistance needs to be less than 30 m<sup>2</sup>K/GW.

The lengthscales of thermal conduction studied in this research are further scaled down to a few nanometers in the final portion of this work. This work measures the thermal properties of the mirror material for extreme ultra-violet (EUV) lithography as the next-generation semiconductor manufacturing technology. The thermal transport across the interfaces of drastically different materials, such as the Mo/Si multilayers (2.8 nm / 4.1 nm), is important in the performance and reliability of the EUV mirrors. This work demonstrates strong anisotropy in the thermal conductivities of the multilayers, where the in-plane conductivity is 13 times higher than the out-of-plane value, owing to the high density of metal-semiconductor interfaces. This research reveals that thermal conduction in such periodic multilayer composites is largely determined by the nonequilibrium electron-phonon physics. A new model indicates that two additional mechanisms – quasi-ballistic phonon transport normal to the metal film and inelastic electron-interface scattering – can also impact conduction in metal-dielectric multilayers with period below 10 nm, the critical length scale for the EUV mirrors.

# Acknowledgments

I am indebted to the many individuals whose support and encouragement made this dissertation possible. I am deeply grateful to my advisor, Professor Kenneth Goodson, for giving me the opportunity and autonomy to pursue my research interests throughout my Ph.D. program. I am immensely indebted to his encouragement, support and patience, especially at times when my research entered difficult phases. I benefited greatly from the opportunity that Professor Goodson provided me to participate in multiple interdisciplinary projects and collaborate with researchers both within and outside Stanford. I would like to thank Professor Mehdi Asheghi for his support and guidance for all my research projects. I greatly enjoyed our numerous discussions which generated some of the best ideas for solving practical problems. Throughout my years at Stanford, I had the privilege to work with Professor Philip Wong on phase change memory. His expertise in semiconductor physics and modern memory devices opened my eyes and helped shape my interest at the intersection of mechanical and electrical regimes. Besides research, I cherish his invaluable advice on my personal and professional development from which I have benefited greatly. I thank members of my dissertation defense committee: Professor James Harris of the Department of Electrical Engineering, Professor Sindy Tang of the Department of Mechanical Engineering, and Professor Alberto Salleo of the Department of Materials Science and Engineering. I highly appreciate their constructive challenges to my thesis research and their valuable feedback which enlightened me on the many interdisciplinary applications of the nanoscale heat transfer. I would like to acknowledge the close collaborations with many individuals on various aspects of this work. I thank John Reifenberg for his mentorship when I first joined the lab. It has been my honor to work with Jaeho Lee, Elah Bozorg-Grayeli, Rakesh Jeyasingh, and Jungwan Cho on our projects for the past several years. I extend my special thanks to Takashi Kodama who helped with the nanofabrication of many samples. I also owe many thanks to my fellow group members for their support, input, and collaborative spirit: Matt Panzer, Jeremy Rowlette, Chen Fang, Milnus David, Julie Steinbrenner, Patricia Gharagozloo, SangBum Kim, Yoonjin Won, Amy Marconnet, Joe Miler, Yuan Gao, Saniya LeBlanc, Shilpi Roy, Sri Lingamneni, Michael Barako, Lewis Hom, Woosung Park, Aditya Sood, Si Tan, Scott Fong, and Ethan Ahn. The phase change memory team at Intel Corporation provided invaluable technical guidance and industrial perspectives, and special thanks to Kuo-Wei Chang, John Kalb, Davide Mantegazza, and Gianpaolo Spadini for the continued partnership over the past years. I would also like to thank Gil Delgado, Matthew Panzer, Alexander Pokrovsky, and Daniel Wack at KLA-Tencor Corporation for providing the samples and technical critics for the molybdenum/silicon multilayers project. In addition, I am grateful to the collaboration with Group4 Labs, Raytheon, and Northrop Grumman on the fundamental research on the high electron mobility transistors. Over the past years, CC Gichane-Bell and Linda Huber have helped me tremendously for all the administrative needs with great kindness and patience. I am also grateful to the Stanford Graduate Fellowship which made my study at Stanford possible, and NSF, SRC, DARPA, Intel, and KLA-Tencor for additional financial support. Finally, I would like to extend my wholehearted thanks to all my friends who have made my life at Stanford so colorful and memorable. I cannot thank family enough for their unconditional love and unwavering support which have inspired me every single day.

# **Table of Contents**

| Table of Conto  | ents                                                                                 | viii |

|-----------------|--------------------------------------------------------------------------------------|------|

| List of Tables  |                                                                                      | xi   |

| List of Figures | 3                                                                                    | xii  |

| Chapter 1: Inti | oduction                                                                             | 1    |

| 1.1 Motiva      | ntion                                                                                | 1    |

| 1.2 Nanoso      | cale Heat Transfer                                                                   | 2    |

| 1.2.1           | Thermal Transport Theories                                                           | 2    |

| 1.2.2           | Thermal Interface Resistance                                                         | 4    |

| 1.3 Electri     | cal Techniques for Thermal Measurement                                               | 9    |

| 1.3.1           | Γhe $3ω$ Technique                                                                   | 10   |

| 1.3.2 \$        | Steady-State Joule Heating Thermometry                                               | 13   |

| 1.3.3           | Suspended Structures for In-Plane Measurements                                       | 16   |

| 1.4 Thesis      | Overview                                                                             | 18   |

| Chapter 2: An   | isotropic Thermal Conduction in Phase Change Memory                                  | 21   |

| 2.1 Introdu     | action                                                                               | 21   |

| 2.2 Therm       | al Conductivity Measurement of Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> Films | 22   |

| 2.2.1           | Experimental Structure Design and Fabrication                                        | 22   |

| 2.2.2           | Measurement Techniques and Procedure                                                 | 25   |

| 2.2.3           | Measurement Results of Anisotropic Thermal Conductivity                              | 28   |

| 2.2.4           | Heat Capacity Measurement of the GST Thin Film                                       | 31   |

| 2.3 Grain S     | Structure and Anisotropy Analysis                                                    | 33   |

| 2.3.1           | Thermal Conductivity Anisotropy                                                      | 33   |

| 2.3.2           | Material Characterization                                                            | 34   |

| 2.3.2           | Modeling the Thermal Conductivity Anisotropy                                         | 37   |

| 2.4 Impact      | s of Anisotropic Thermal Conduction on Device Performance                            | 40   |

| 2.4.1           | Thermal Disturbance and Minimum Cell Spacing                                         | 40   |

| 2.4.2           | Programming Current of PCM Devices                                                   | 41   |

| 2.5 Sumn     | nary and conclusions                                            | 43   |

|--------------|-----------------------------------------------------------------|------|

| Chapter 3: M | fultibit Phase Change Memory Analysis and Design Strategy       | 44   |

| 3.1 Introd   | luction                                                         | 44   |

| 3.2 Electr   | othermal Modeling and Simulation                                | 46   |

| 3.2.1        | Electrical, Thermal, and Phase Transition Models and Algorithms | s 46 |

| 3.2.2        | Simulation results of SET and RESET Operations                  | 49   |

| 3.2.3        | Comparison between Simulation and TEM Images                    | 52   |

| 3.2 Multi    | bit PCM Performance Analysis                                    | 55   |

| 3.2.1        | Tail Duration-Controlled Mushroom Cell                          | 56   |

| 3.2.2        | Amplitude-Controlled Confined Pillar Cell                       | 57   |

| 3.3 Nove     | l Cell Structure and Multibit Design Strategy                   | 60   |

| 3.4 Sumn     | nary and Conclusions                                            | 63   |

| Chapter 4: H | igh Electron Mobility Transistor                                | 64   |

| 4.1 Introd   | luction                                                         | 64   |

| 4.2 Mater    | rial Properties and Thermal Modeling                            | 65   |

| 4.2.1        | Thermal Properties of HEMT Constituent Materials                | 65   |

| 4.2.2        | Numerical Modeling                                              | 67   |

| 4.2.3        | Model Calibration and Comparison with Measurement Data          | 69   |

| 4.3 Therr    | nal Characterization Using Nanoheaters                          | 71   |

| 4.3.1        | Sample Preparation and DC Joule Heating Thermometry             | 71   |

| 4.3.2        | Thermal Conductivity Measurement of GaN Buffer Layer            | 74   |

| 4.3.3        | GaN-Diamond Thermal Interface Resistance Measurement            | 76   |

| 4.4 Impa     | ct of Diamond Substrate on Near Junction Thermal Transport      | 78   |

| 4.4.1        | HEMT Thermal Resistance Decomposition                           | 78   |

| 4.4.2        | Comparison between HEMT with SiC and Diamond Substrates         | 80   |

| 4.4.3        | GaN-on-Diamond with and without Transition Layers               | 81   |

| 4.4.4        | Target Value of GaN-Diamond Thermal Interface Resistance        | 82   |

| 4.5 Sumn     | nary and Conclusions                                            | 84   |

| Chapter 5: U | ltrathin Mo/Si Multilayers                                      | 85   |

| 5.1 Heat     | Transfer in Metal/Semiconductor Multilayers                     | 85   |

| 5.2 Anisot    | tropic Thermal Conductivity Measurement                         | 86  |

|---------------|-----------------------------------------------------------------|-----|

| 5.2.1         | Mo/Si Multilayer Sample Preparation                             | 86  |

| 5.2.2         | Measurement and Results                                         | 87  |

| 5.3 Therm     | al Modeling of Metal/Dielectric Multilayers                     | 91  |

| 5.3.1         | Electron-Phonon Nonequilibrium                                  | 92  |

| 5.3.2         | Direct Phonon Transmission                                      | 94  |

| 5.3.3         | Inelastic Electron-Interface Scattering                         | 96  |

| 5.4 Summ      | ary and Conclusions                                             | 99  |

| Chapter 6: Co | ncluding Remarks                                                | 100 |

| 6.1 Summ      | ary of Dissertation                                             | 100 |

| 6.2 Sugge     | stions for Future Work                                          | 102 |

| 6.2.1         | Compositional diffusion in chalcogenide materials for PCM       | 102 |

| 6.2.2         | Fully-Coupled Multiphysics Modeling for PCM                     | 104 |

| 6.2.3         | Measurement of Inelastic Electron-Interface Scattering in Mo/Si | 104 |

| Bibliography. |                                                                 | 106 |

# List of Tables

| Number Page                                                                                         |

|-----------------------------------------------------------------------------------------------------|

| Table 1. XRD peak intensities of different forms of GST                                             |

| Table 2. Electrical conductivity $\sigma$ , thermal conductivity $k$ , and heat capacity $C$ of the |

| electrode and insulator materials used in the simulation                                            |

| Table 3. Structures of 2 <sup>nd</sup> Generation GaN-on-Diamond Samples and Thermal                |

| Resistance Data for the Adhesion Layer                                                              |

| Table 4. Effective cross-plane thermal conductivities of two multilayer samples with                |

| different Mo thickness fraction ( $\Gamma = d_{Mo}/d_{total}$ ). Theoretical calculations           |

| agree with the measurement data                                                                     |

| Table 5. Material properties of molybdenum used in the calculation                                  |

# List of Figures

| Number    | Page                                                                                                     |

|-----------|----------------------------------------------------------------------------------------------------------|

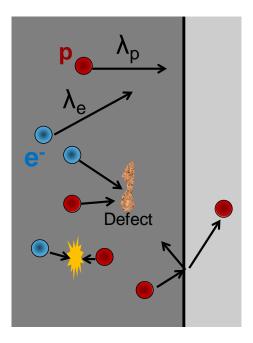

| Figure 1. | Schematic of the energy carriers in solids and their interactions. Phonons                               |

|           | (P) and electrons (e) are the relevant heat carriers in the solids, and their                            |

|           | mean free paths ( $\lambda_p$ and $\lambda_e$ ) describe the average distance the carriers travel        |

|           | between scattering events. Nanomaterials and nanostructures often feature                                |

|           | characteristic length scales that are smaller than the mean free path, a                                 |

|           | situation where the classical heat diffusion theory is no longer applicable. 4                           |

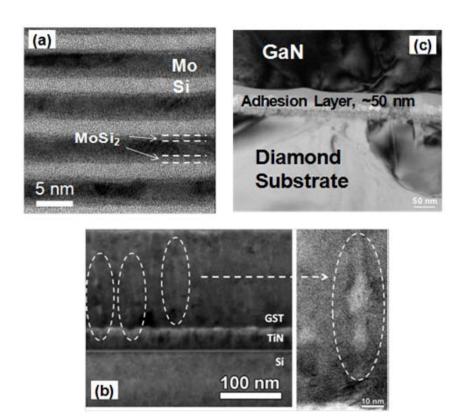

| Figure 2. | Transmission electron microscope (TEM) images of the three types of                                      |

|           | interfaces studied in this work. (a) Material boundaries: interfaces between                             |

|           | alternating Mo and Si thin films which are used as extreme ultraviolet                                   |

|           | mirrors [21]. (b) Phase boundaries: interfaces between the crystalline and                               |

|           | amorphous regions in a Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> thin film for phase change memory |

|           | [25]. (c) Interfacial material layer: disordered adhesion layer between GaN                              |

|           | and diamond substrate for high electron mobility transistors                                             |

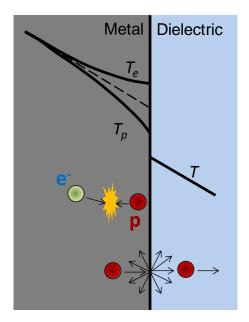

| Figure 3. | Illustration of the two-temperature model (TTM). Temperatures of the                                     |

|           | electron system ( $T_e$ ) and the phonon system ( $T_p$ ) in the metal side deviates                     |

|           | from each other near the metal-dielectric interface. Thermal energy carried                              |

|           | by the electrons must first be transferred to the phonons in the metal layer                             |

|           | before being carried to the dielectric side by the phonons                                               |

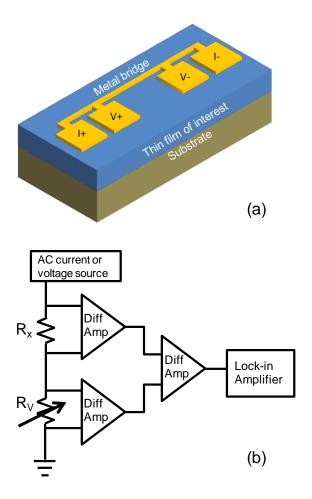

| Figure 4. | Schematic of a typical setup for $3\omega$ measurements. (a) schematic of a                              |

|           | sample structure. Metal bridges with a 4-probe configuration are fabricated                              |

|           | on top of the thin film. Passivation layers (not shown) may be necessary                                 |

|           | between the metal pattern and the thin film, as well as between the thin                                 |

|           | film and the substrate. (b) a typical measurement circuit using differential                             |

|           | amplifiers. The sample and a variable resistor are denoted as $R_x$ and $R_y$ ,                          |

|           | manuscriptorius 11                                                                                       |

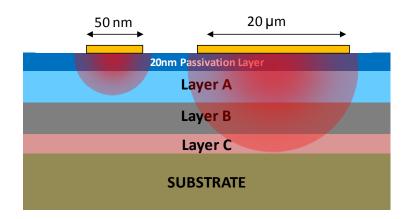

| Figure 5. | Schematic of a multilayer structure and heater bridges with varying widths.                        |

|-----------|----------------------------------------------------------------------------------------------------|

|           | Narrow heaters confine the heat within a shallow region below the surface,                         |

|           | and their temperature rise is not sensitive to the thermal properties of the                       |

|           | layers further below. The heat generated from the wide heaters probes                              |

|           | deeper into the multilayer stack. Schematic is not drawn to scale 14                               |

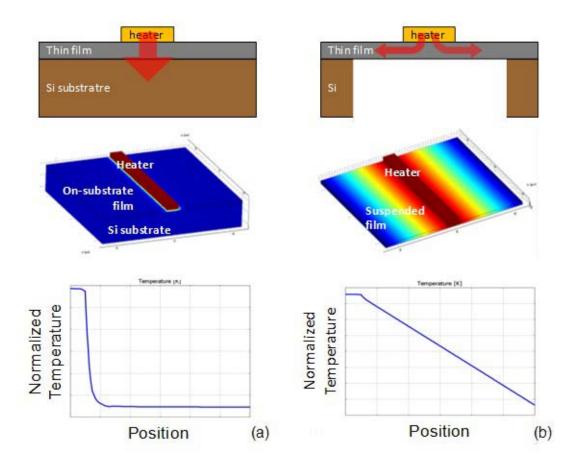

| Figure 6. | Temperature distribution of on-substrate and suspended structures. Top:                            |

|           | schematics of the sample structures. Middle: numerical simulation of the                           |

|           | temperature distributions. Bottom: temperature profile at the top surface in                       |

|           | the lateral direction from the center of the heater to the edge of the sample                      |

|           | (heat sink). (a) On-substrate structures usually show limited sensitivity to                       |

|           | the in-plane conduction when the heater is much wider than the thickness                           |

|           | of the thin film. (b) Suspended structures force all the heat to dissipate                         |

|           | laterally and are therefore highly sensitive to the in-plane thermal                               |

|           | conductivity of the thin film                                                                      |

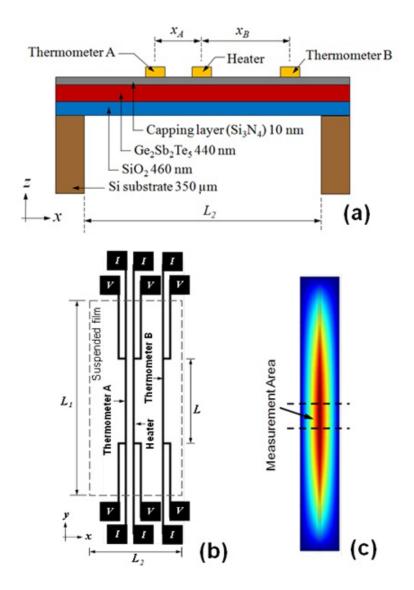

| Figure 7. | Schematic of the experimental structure with suspended GST thin film. (a)                          |

|           | Cross-sectional view of the structure. The width of the heater and                                 |

|           | thermometers are 2 $\mu$ m, and the distances $x_A$ and $x_B$ vary from 20 $\mu$ m to              |

|           | 160 µm; (b) Top-view of the front side patterns. The example dimensions                            |

|           | of the suspended film are $L_1 = 3200 \ \mu \text{m}$ and $L_2 = 400 \ \mu \text{m}$ . Measurement |

|           | area is located in the center of the membrane with a length of $L = 200 \mu m$ .                   |

|           | (c) Finite-Element simulation of the temperature distribution of the                               |

|           | suspended thin film. The 8:1 length-to-width ratio provides a one-                                 |

|           | dimensional temperature gradient in the x-direction. Figures are not drawn                         |

|           | to scale. 23                                                                                       |

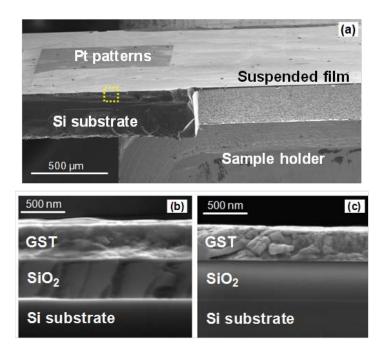

| Figure 8. | Scanning Electron Microscopy (SEM) images of the experimental structure                            |

|           | with suspended thin film. (a) Part of the sample near one end of the                               |

|           | suspended thin film; (b) Magnified image of the dotted region in (a) with                          |

|           | as-deposited a-GST thickness of 440 nm; (c) Crystalline f-GST is obtained                          |

|           | by annealing the sample at 150°C. The thickness of f-GST film is reduced                           |

|           | to 409 nm due to the increase in density upon crystallization                                      |

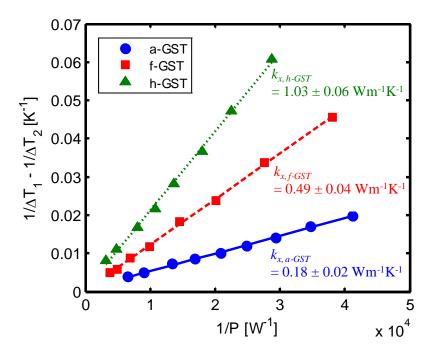

| Figure 9.  | Data of the in-plane thermal conductivity measurement. The solid, long-                       |

|------------|-----------------------------------------------------------------------------------------------|

|            | dashed and short-dashed lines are the linear fit of a-GST, f-GST and h-                       |

|            | GST, respectively. The slopes of these fitted straight lines give the values                  |

|            | of in-plane thermal conductivities of the GST thin film at different phases.                  |

|            | Uncertainty of each data point is less than 0.002 K <sup>-1</sup>                             |

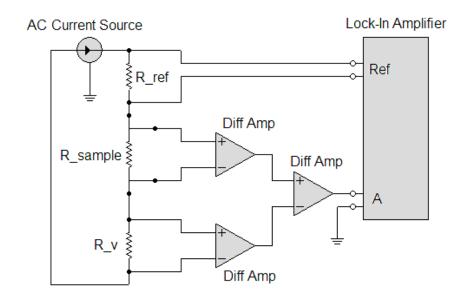

| Figure 10. | Electrical circuit for the $3\omega$ measurement. R_sample is the resistance of               |

|            | the $3\omega$ structure and $R\_v$ is a variable resistor with low thermal coefficient        |

|            | of resistivity (TCR). The amplitude and phase of the voltage signal at $3\boldsymbol{\omega}$ |

|            | frequency is captured by a lock-in amplifier                                                  |

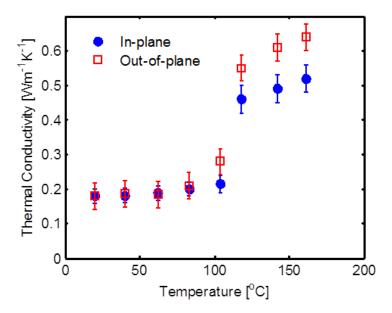

| Figure 11. | Temperature-dependent in-plane and out-of-plane thermal conductivities                        |

|            | of the GST thin film. Thermal conductivity anisotropy begins to appear at                     |

|            | the transition from a-GST to f-GST                                                            |

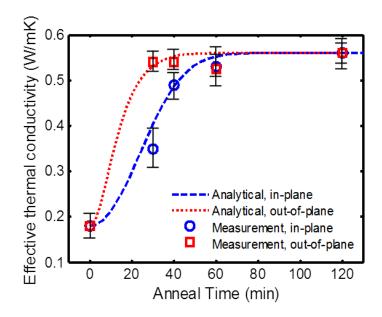

| Figure 12. | Data for the in-plane and out-of-plane thermal conductivities of GST films,                   |

|            | summarized here based on a full-length article [6], and compared with the                     |

|            | model developed in this work. The amorphous GST was annealed at                               |

|            | $150~^{\circ}\mathrm{C}$ for each time duration                                               |

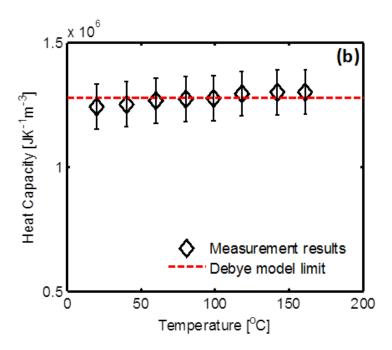

| Figure 13. | Heat capacity measured by the suspended structure and the theoretical                         |

|            | limit calculated by Debye model for heat capacity                                             |

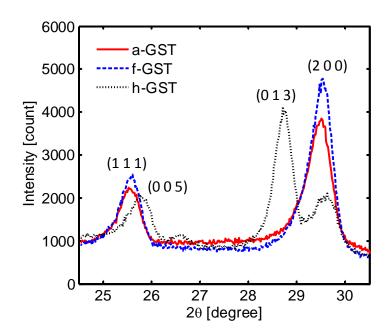

| Figure 14. | X-ray diffraction (XRD) patterns of a-GST, f-GST, and h-GST. The a-GST                        |

|            | is annealed near the phase transition temperature to show a weaker cubic                      |

|            | pattern. h-GST exhibits a strong hexagonal (0 1 3) peak and diminished                        |

|            | cubic (2 0 0) peak. The intensities of the peaks are compared with data                       |

|            | from GST powder sample                                                                        |

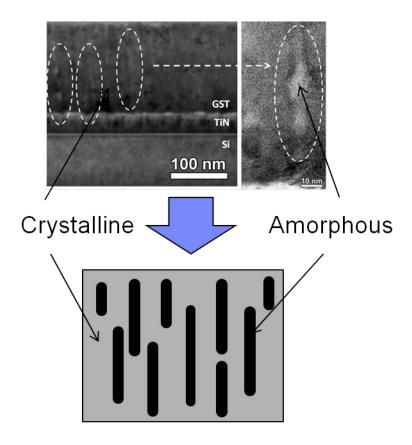

| Figure 15  | Grain structures of the polycrystalline GST film. Top: transmission                           |

|            | electron microscope (TEM) image of the polycrystalline GST film.                              |

|            | Amorphous regions are found between the grain boundaries and are                              |

|            | aligned in the out-of-plane direction. The TEM image is from our work                         |

|            | described in [25]. Bottom: an abstraction of the mixed-phase grain                            |

|            | structures where discrete, vertically-aligned amorphous regions are                           |

|            | dispersed among a continuous crystalline phase                                                |

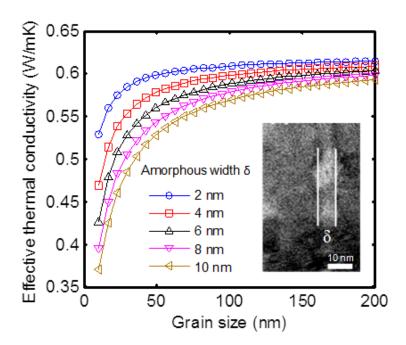

| Figure 16. | Calculated effective thermal conductivities of f-GST as a function of grain       |

|------------|-----------------------------------------------------------------------------------|

|            | size. The extent of the amorphous region $(\delta)$ between crystalline grains is |

|            | estimated from TEM image [25]                                                     |

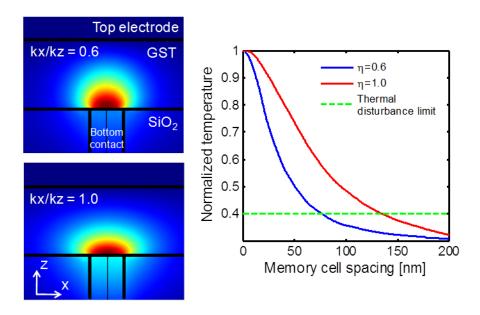

| Figure 17. | Electro-thermal simulation results. (a) Temperature distribution during           |

|            | reset operation of a PCM cell with anisotropic and isotropic GST layers of        |

|            | 100 nm. (b) Normalized temperature profile along the GST layer in the $x$         |

|            | direction. Thermal disturbance limit is set close to the phase transition         |

|            | temperature neglecting cyclic effects                                             |

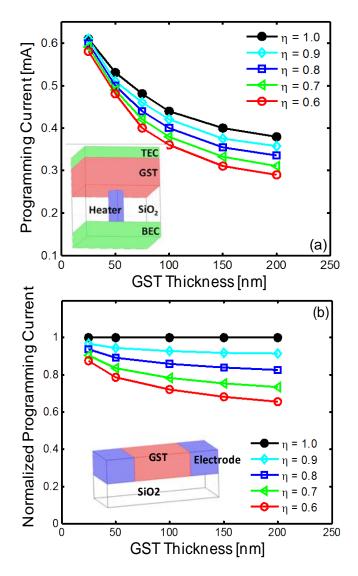

| Figure 18. | Programming current during a reset operation as a function of GST film            |

|            | thickness and thermal conductivity anisotropy. (a) Programming current of         |

|            | a vertical phase change memory cell. Inset: schematic of the vertical cell        |

|            | including bottom electrode contact (BEC) and top electrode contact (TEC)          |

|            | used for simulation. (b) Programming current of a lateral line-shaped cell.       |

|            | Inset: lateral cell used in the simulation                                        |

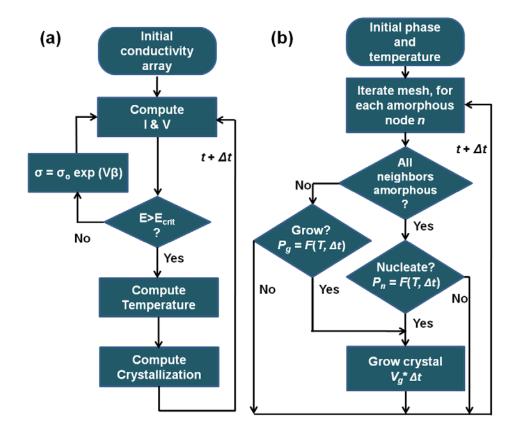

| Figure 19. | Key computational flows implemented in the coupled simulation. (a)                |

|            | Electrical model compares the local electrical field with the critical field      |

|            | before solving for the temperature and phase; (b) GST crystallization             |

|            | algorithm considers two parallel mechanisms: probabilistic nucleus                |

|            | formation and crystalline growth, both as functions of cell temperature $T$       |

|            | and time duration $\Delta t$                                                      |

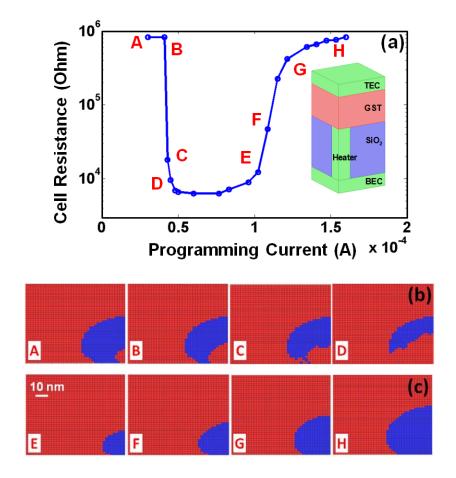

| Figure 20. | Simulation results of phase transitions in a mushroom-shaped PCM device.          |

|            | (a) Simulated R-I characteristics of a PCM cell for different programming         |

|            | currents. SET operation occurs in A through D, while E through H                  |

|            | correspond the RESET process. Inset: schematic of the PCM cell; (b)               |

|            | Cross-sectional view of the GST phase distribution after a SET operation          |

|            | with different current amplitude; (c) GST phase distribution after a RESET        |

|            | process with varying current amplitude. Red and blue colors represent             |

|            | crystalline and amorphous phases, respectively                                    |

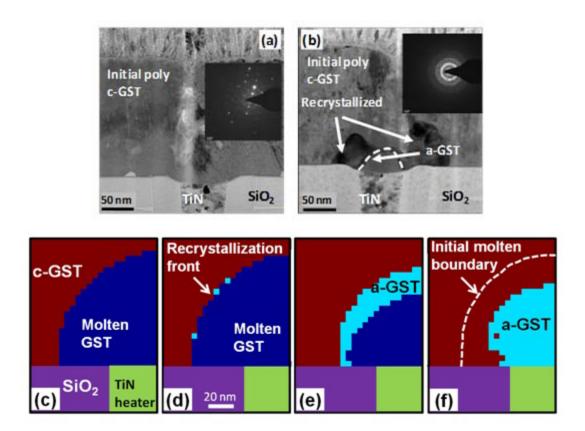

| Figure 21. | Comparison of transmission electron microscopy (TEM) images and the               |

|            | simulated phase distribution after RESET pulses. Cross-sectional TEM              |

| image are taken with a similar device in a previous study in [122]. (a) The          |

|--------------------------------------------------------------------------------------|

| GST film is polycrystalline (c-GST) in the initial SET state as confirmed            |

| by the electron diffraction pattern in the inset. (b) Amorphous GST (a-              |

| GST) cap is formed on top of the TiN heater after RESET operation. The               |

| inset shows the electron diffraction pattern corresponding to the a-GST cap          |

| region. (c)-(f) Simulated transient phase distribution during a partial              |

| RESET process. The area between the initial molten region and the final a-           |

| GST cap resulted from recrystallization process explains the different               |

| crystalline texture around the a-GST cap                                             |

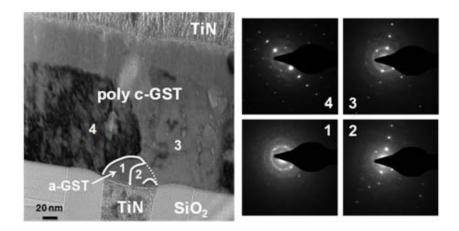

| figure 22. Filament-like crystallization of a PCM cell after partial SET pulses. The |

| cross-sectional TEM images are taken in a previous study [124]. The                  |

| amorphous region 1 is marked by dashed lines. A thick filament region 2 of           |

| crystalline nature is seen between the amorphous regions. Regions 3 and 4            |

| are polycrystalline as confirmed by the electron diffraction pattern. This           |

| filament growth pattern, possibly due to material inhomogeneity and                  |

| defects, is not captured by the current simulation                                   |

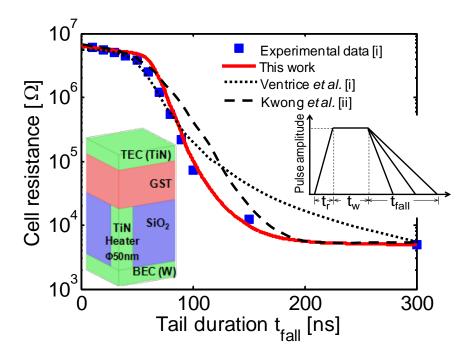

| figure 23. Mushroom cell resistance as a function of the tail duration of a RESET    |

| current pulse. Experimental data are taken from i-[109]. This work                   |

| achieves improved prediction of the transitional behavior of the cell                |

| resistance compared with two other models proposed in i-[109] and ii-                |

| [111]. Inset: mushroom cell schematic used in this simulation, and the               |

| shape of a RESET pulse                                                               |

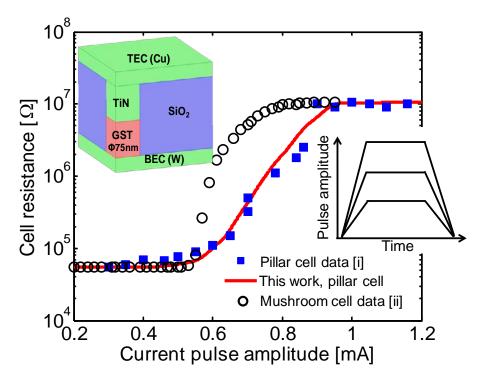

| Figure 24. Amplitude-controlled cell resistance after a RESET current pulse.         |

| Experimental data of the confined pillar cell are taken from i-[127]. The            |

| simulated intermediate resistances match reasonably well with measured               |

| resistance evolution. The pillar cell yields more gradual resistance change          |

| comparing to a mushroom cell controlled by the same amplitude-based                  |

| scheme ii-[120]. Inset: confined pillar cell schematic, and the shape of             |

| RESET pulses with varying amplitudes59                                               |

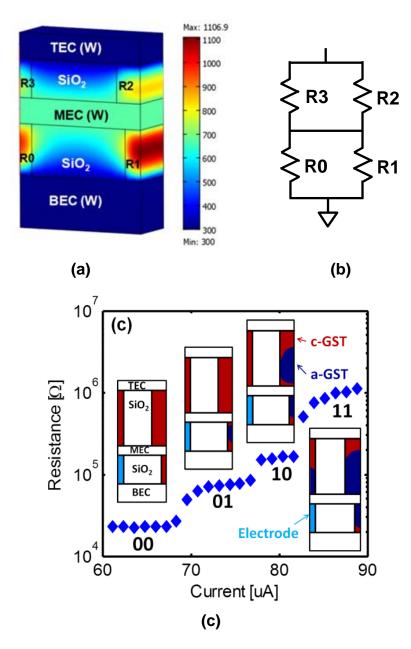

| Figure 25. | Stacked vertical multibit cell. (a) A schematic and representative                |

|------------|-----------------------------------------------------------------------------------|

|            | temperature distribution of the cell. (b) Electrical model in which the           |

|            | heating power is decoupled between the two floors. (c) Simulation results         |

|            | of the multibit programming with four distinct resistance levels. Insets:         |

|            | device cross-section view and phase distributions at each of the four             |

|            | resistance levels. Red and dark blue corresponds to c-GST and a-GST,              |

|            | respectively. The heating element (light blue) is a tungsten electrode 62         |

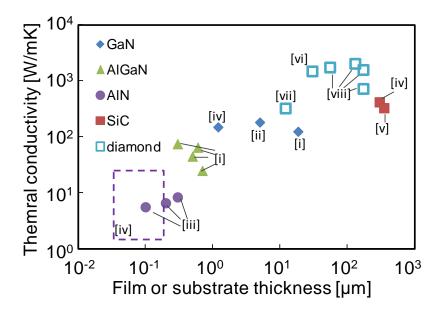

| Figure 26. | Representative cross-plane thermal conductivity data for the materials in         |

|            | AlGaN/GaN HEMT devices. Data are selected from the following                      |

|            | references: i-[150], ii-[151], iii-[152], iv-[145], v-[146], vi-[147], vii-[148], |

|            | viii-[149], iv-[143]66                                                            |

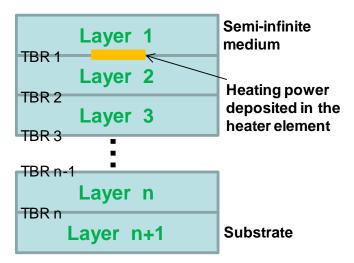

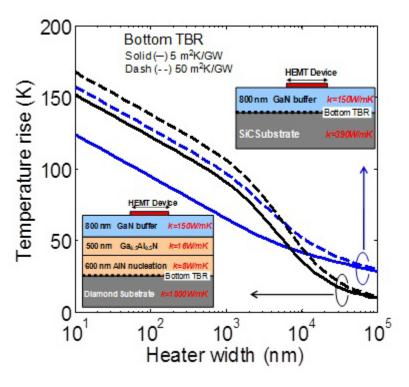

| Figure 27. | Multilayer HEMT model for thermal simulation. The heating power is                |

|            | deposited to the heater element with varying dimensions                           |

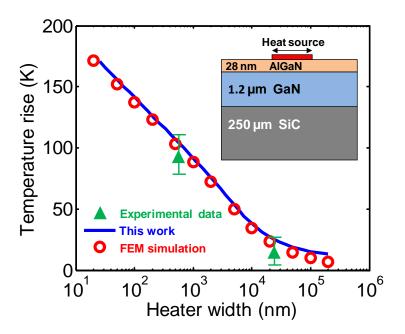

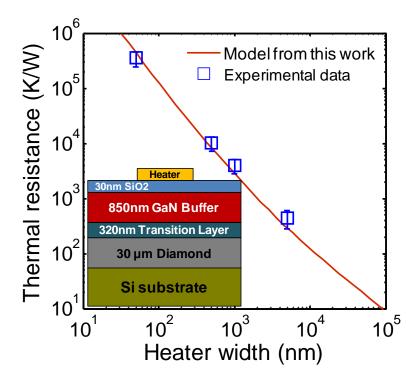

| Figure 28. | Comparison of the semianalytical HEMT thermal model with finite                   |

|            | element method (FEM) simulation COMSOL and the experimental data                  |

|            | from [141]. Our simplified model achieves good agreement for length               |

|            | scales smaller than 100 µm                                                        |

| Figure 29. | Simulated and measured thermal resistances seen by different heating              |

|            | source on a multilayer HEMT test structure. The experimental data are             |

|            | taken with the nanoheater measurement in this work                                |

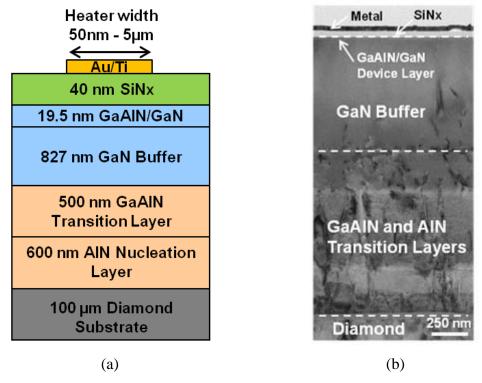

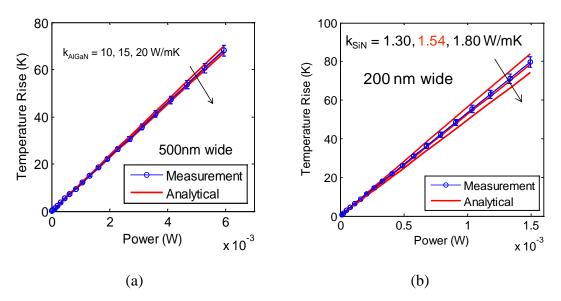

| Figure 30. | Layer structure and thicknesses of a representative HEMT sample. (a)              |

|            | Cross sectional schematic of the sample structure with nanoheater bridges         |

|            | deposited on the top; (b) TEM image of the sample stack71                         |

| Figure 31. | SEM image of a top view of the fabricated nanoheaters by e-beam                   |

|            | lithography. Heater width of the sample varies from 50 nm to 5 $\mu$ m 72         |

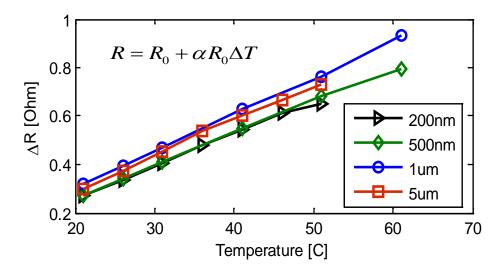

| Figure 32. | Calibration of TCR for four different heater widths. Due to the fabrication       |

|            | variations of the nanoheaters, the calibration process is performed before        |

|            | each measurement                                                                  |

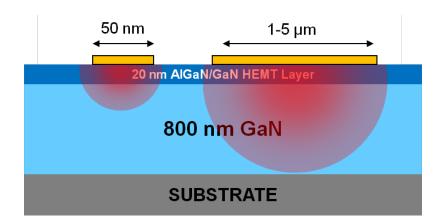

| Figure 33. | Spatial confinement by varying heater widths. Narrower heaters (50nm)             |

|            | confines the heat in a shallow layer on the top and is more sensitive to the      |

|            | lateral heat spreading, while wider heaters are less sensitive to the in-plane        |

|------------|---------------------------------------------------------------------------------------|

|            | thermal conductivity of the 20 nm HEMT layer                                          |

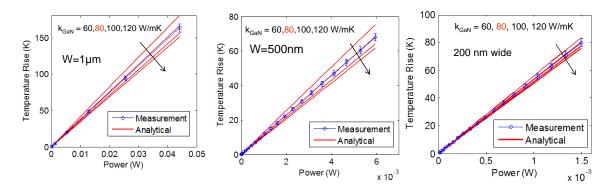

| Figure 34. | Parametric fitting of an analytical heat conduction model to the self-                |

|            | heating data for the heater bridge with width of 200, 500 and 1000 nm                 |

|            | yield consistant results ( $\sim 80~W/mK$ ) for thermal conductivity of GaN           |

|            | buffer layer                                                                          |

| Figure 35. | Verification of the assumptions made in the measurement. (a) Low                      |

|            | sensitivity of the nanoheaters to the bottom transition layer. The                    |

|            | theoretical temperature rises do not change beyond the uncertainty bar of             |

|            | the measurement data when varying $k_{\text{AlGaN}}$ by $\pm$ 50%. (b) Cross check of |

|            | the thermal conductivity of SiN using data from the DC Joule heating                  |

|            | measurement. The value of 1.54 W/mK from thermal reflectance                          |

|            | measurement achieves fairly good fit to the analytical solution                       |

| Figure 36. | 2 <sup>nd</sup> generation HEMT structure with removed AlN nucleation layer and       |

|            | much reduced transition layer thickness                                               |

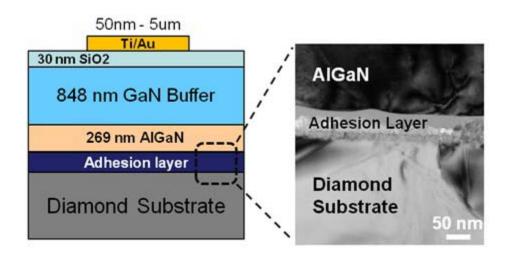

| Figure 37. | Thermal resistance decomposition. The GaN layer and thermal interface                 |

|            | resistance are the major contributors to the total thermal resistance in the          |

|            | single-finger and multifinger length scales, while the substrate dominates            |

|            | in the package level                                                                  |

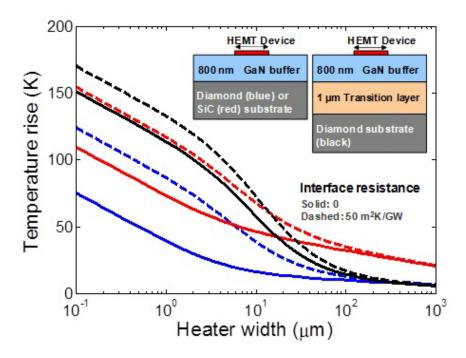

| Figure 38. | Comparison between SiC substrate and diamond substrate. Relevant TBRs                 |

|            | are included in the simulation                                                        |

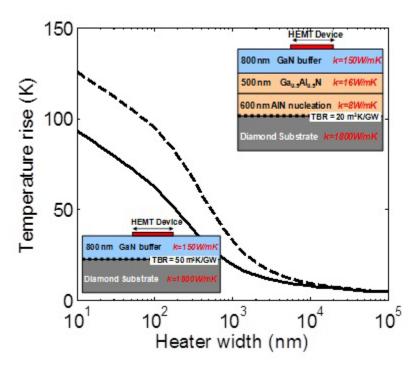

| Figure 39. | Performance improvement of the GaN-on-diamond configuration obtained                  |

|            | by removing the GaAlN and AlN transition layers                                       |

| _          | Simulated temperature rises of HEMT on SiC substrates (red), diamond                  |

|            | with transition layer (black), and diamond without transition layer (blue)            |

|            | for a power dissipation of 6 W/mm. Inset: schematics of the HEMT                      |

|            | structures. Figures are not drawn to scale                                            |

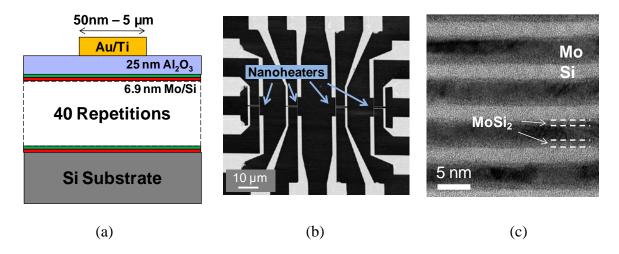

| Figure 41. | Mo/Si multilayer sample and nanoheater patterns. (a) Schematic of the 40              |

|            | repetitions of Mo/Si multilayer. (b) Scanning electron microscope (SEM)               |

|            | image of the e-beam patterned Au nanoheaters with width ranging from 50               |

|            | nm to 5 µm (not all widths are shown in the graph). (c) Transmission                                  |

|------------|-------------------------------------------------------------------------------------------------------|

|            | electron microscope (TEM) image of the Mo/Si multilayer. A thin MoSi <sub>2</sub>                     |

|            | layer of 0.5~1.2 nm is formed between Mo and Si due to atomic diffusion.87                            |

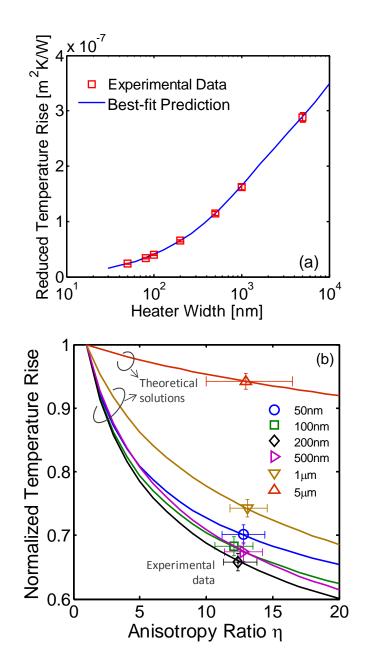

| Figure 42. | Electrical thermometry data and comparison with best-fit predictions for                              |

|            | the Mo/Si multilayer with Mo thickness fraction of $\Gamma=0.4$ . (a) Reduced                         |

|            | temperature rise for different heater widths. (b) Thermal conductivity                                |

|            | anisotropy ratio $\eta = k_x/k_z$ is measured with multiple heater widths. The                        |

|            | measured anisotropy ratio (~13) is consistent among all the heater length                             |

|            | scales90                                                                                              |

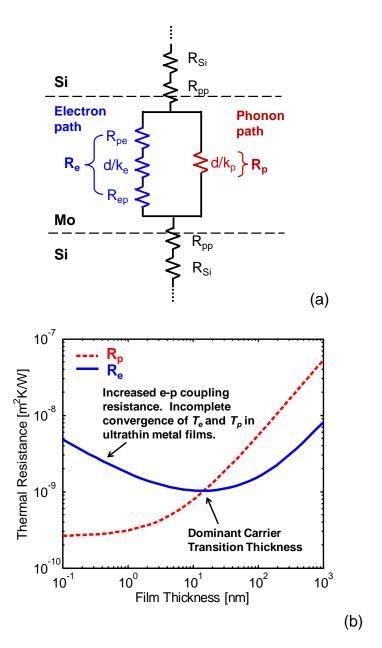

| Figure 43. | Thermal resistances in the Mo/Si multilayer system. (a) Approximate                                   |

|            | thermal resistance network model where the conduction in the Mo layer                                 |

|            | consists of a parallel of the electron path and the phonon direct                                     |

|            | transmission path. (b) Theoretical calculation result shows that the thermal                          |

| Figure 44  | resistance of the phonon path $(R_p)$ becomes smaller than the electron path                          |

|            | $(R_e)$ for a metal film thickness of less than $d_{trans} = 14$ nm                                   |

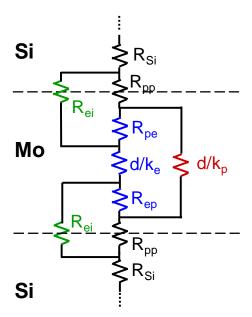

| Figure 44. | Complete thermal resistor network of the metal-semiconductor multilayers.                             |

| riguie 44. | Three physical mechanisms are included: electron-phonon nonequilibrium                                |

|            | $(R_{pe} \text{ and } R_{ep})$ , direct phonon transport $(d/k_p)$ , and inelastic electron-interface |

|            | scattering ( <i>R<sub>ei</sub></i> )                                                                  |

# Chapter 1: Introduction

### 1.1 Motivation

Thermal conduction has become a critical consideration in the design and operation of many micro- and nanodevices. Advances in semiconductor devices over the past decade have generated a variety of unique structural and material properties in the nanometer length scales. The rapid reduction in the size of semiconductor devices requires improved understanding of heat conduction mechanisms involving complex nanostructures and interfaces. Classical heat transfer theory is largely based on a thermal equilibrium approach and an assumption of continuum behavior. At the nanoscale, however, the transfer of thermal energy may not be an equilibrium process and materials can exhibit non-continuum behavior. This is especially important when the device size or material structural characteristic lengths approach the mean free paths of the corresponding energy carriers (electrons and phonons), or when the timescale of interest is on the order of the thermal relaxation time of the energy carriers. In addition, progress in the design and synthesis of nanostructured materials has provided an opportunity to engineer the electrical, thermal, and phase change properties on the nanometer length scale in order to achieve unique device performance which is unattainable at longer length scales. Therefore, detailed studies of nanoscale heat transfer mechanisms are of fundamental importance to the continued development of nanostructured semiconductor materials and devices.

Three types of thermal transport problems are of particular interest for semiconductor nanodevices and materials. One is to utilize and manipulate the highly localized, intense heat flux in the nanodevices for applications such as data storage and energy conversion. Examples include phase change memory [1-3] and thermoelectric devices [4-6]. Another important area lies in the thermal management of semiconductor devices. Specifically, the continued scaling down of integrated circuits and increasing power density of electronic chips require advanced technology to remove the heat efficiently from the near-junction region where the characteristic

length scale ranges from several nanometer to several micrometer [7, 8]. Finally, the fundamental physics of the nanoscale thermal conduction and its impact on nanostructured materials have received increasing attention. For examples, nanometer sized hot spots can degrade the material and reduce device reliability due to localized thermal expansion [9] or atomic diffusion between the adjacent materials [10]. This thesis makes experimental and theoretical progresses in these areas in the context of specific applications including phase change memory, high electron mobility transistors, and ultrathin Mo/Si multilayer for extreme ultraviolet mirrors.

### 1.2 Nanoscale Heat Transfer

#### 1.2.1 Thermal Transport Theories

In this work, heat transfer in solids is studied at two levels of detail and rigor: classical heat diffusion theory and kinetic theory. Classical heat diffusion theory, while less detailed, is often sufficiently rigorous for many thermal transport problems. Fourier's Law states that the heat flux in a certain direction is proportional to the negative temperature gradient along that direction:

$$\vec{q}" = -\vec{k} \cdot \nabla T , \qquad (1)$$

where T is the local temperature,  $\vec{q}$  " is the heat flux, and  $\vec{k}$  is the thermal conductivity of the medium. The application of the Fourier's Law to a three-dimensional medium without internal heat generation yields the classical heat diffusion equation:

$$\frac{1}{D}\frac{\partial T}{\partial t} = \eta \left(\frac{\partial^2 T}{\partial x^2} + \frac{\partial^2 T}{\partial y^2}\right) + \frac{\partial^2 T}{\partial z^2},\tag{2}$$

where D is the thermal diffusivity, t is time, and x, y, z are the dimensional coordinates. Because thin films in nanodevices often have different thermal conductivities along the in- and out-of-plane directions, the heat diffusion equation is modified with an anisotropy ratio  $\eta = k_x/k_z$ . Equation (2) is useful for bulk materials, as well as in thin film materials as long as the characteristic length scale is much larger

than the mean free path of the heat carriers. When using this classical heat transfer approach, details of energy carriers (phonons, electrons) are lumped together into the macroscopic properties (*e.g. D, k*, and  $\eta$ ). The thermal modeling for the multibit phase change memory (Chapter 3) is mainly based on classical heat diffusion theory because the characteristic dimensions of the device (tens to hundreds of nanometers) are much larger than the phonon mean free path in the phase change material (~1 nm).

Kinetic theory, a more detailed treatment of thermal transport, considers the microscopic behavior and interactions of the energy carriers [11]. Electrons and phonons travel with known velocities and scatter with each other, and at a variety of imperfections including dopants, material defects, phase and grain boundaries, and material interfaces as shown in Figure 1. The mean free path describes the average distance that an energy carrier travels between two scattering events. Classical heat diffusion theory is no longer applicable when the characteristic length scale of the device becomes comparable or smaller than the mean free paths of the relevant heat carriers. For this reason, the theoretical modeling of most nanostructured materials in this thesis is built on the platform of the kinetic theory. The Boltzmann transport equation (BTE), derived from kinetic theory, keeps track of the number balance of the energy carriers and the scattering events in order to model thermal transport. This work mainly studies heat transfer in nanostructures in the absence of external electric forces, in which case the BTE can be written as [12]:

$$\frac{\partial f}{\partial t} + \mathbf{v} \cdot \nabla_{\mathbf{r}} f = \left(\frac{\partial f}{\partial t}\right)_{\text{scat}},\tag{3}$$

where f is the distribution function of the particles,  $\mathbf{v}$  is the group velocity vector, and the subscript  $\mathbf{r}$  denotes the physical space. The BTE provides a powerful tool to study the detailed transport behavior of electrons and phonons within a medium [13-16] and also the heat transfer behavior across material boundaries [17, 18].

Figure 1. Schematic of the energy carriers in solids and their interactions. Phonons (P) and electrons (e<sup>-</sup>) are the relevant heat carriers in the solids, and their mean free paths ( $\lambda_p$  and  $\lambda_e$ ) describe the average distance the carriers travel between scattering events. Nanomaterials and nanostructures often feature characteristic length scales that are smaller than the mean free path, a situation where the classical heat diffusion theory is no longer applicable.

#### 1.2.2 Thermal Interface Resistance

Thermal interface resistances are increasingly important as device dimensions scales down, and they can become the dominant contributor of the overall thermal resistance of nanostructured devices [19-21]. The thermal interface resistance between solids,  $R_b$ , is defined as

$$R_b = \frac{\Delta T}{q''} \tag{4}$$

where  $\Delta T$  is the temperature drop across the interface. The term "interface" in this thesis is a broad concept and covers a variety of interfaces. One of the most common

interfaces is the material boundary which is formed by putting two media into contact, as shown in Figure 2(a). Electrons or phonons must travel from one material, across the interface, and into the other side in order for the heat to flow. Energy exchange between heat carriers is required if the dominant carriers are different in the two adjacent media, which introduces an additional resistance to the heat flow [14, 22-24]. Another type of interface involves the boundary between different crystalline phases, which occurs in some phase change materials (Figure 2(b)). For example, Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> film can have a mixture of crystalline and amorphous phases under certain annealing conditions [25, 26]. If the crystalline grains are preferentially oriented in the out-ofplane direction, the phonons traveling in the in-plane direction scatter more frequently at the grain boundaries. The inhomogeneity of the material structure can cause anisotropic thermal conductivities along the two directions. A third type of interface studied in this work is, in fact, an interfacial layer connection two functional materials. One example is the GaN high electron mobility transistor (HEMT) with diamond substrate [27, 28]. The high thermal conductivity of diamond makes it attractive for cooling of HEMT devices. However, an adhesion layer is required between the diamond substrate and the GaN due to the fabrication process. Figure 2(c) shows the transmission electron microscope (TEM) image of region near the GaN-diamond Measuring the thermal resistance associated with the thin layers of interface. disordered adhesive material helps improve the effectiveness of the thermal management for the HEMT devices. For clarity of discussion, this dissertation uses the term "thermal boundary resistance (TBR)" for the first two types of interfaces where the two functional materials are in direct contact, and uses the term "effective thermal interface resistance" to denote the third type of interface where another thin adhesion layer is involved.

Figure 2. Transmission electron microscope (TEM) images of the three types of interfaces studied in this work. (a) Material boundaries: interfaces between alternating Mo and Si thin films which are used as extreme ultraviolet mirrors [21]. (b) Phase boundaries: interfaces between the crystalline and amorphous regions in a Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> thin film for phase change memory [25]. (c) Interfacial material layer: disordered adhesion layer between GaN and diamond substrate for high electron mobility transistors.

Several theories on the physics of TBR have been developed in the past several decades. The diffuse mismatch model (DMM) is commonly used to evaluate the thermal conductance due to phonon-phonon coupling across an interface [17, 29-31]. The DMM assumes diffusive phonon reflection at interfaces, which is typically valid at the room temperature where the phonon wavelength is shorter than the interface roughness. Assuming the temperature drop across the interface is small, the thermal interface conductance is [31]

$$h_{pp,1-2} = \left(\frac{\alpha_{1-2}}{12} v_{1,D}^3 \sum_{j} v_{1,j}^{-2}\right) C_{1,\nu}(T), \tag{5}$$

where  $C_v(T)$  is volumetric heat capacity at T, and v is the speed of sound with its subscript j denoting the polarization (I for longitudinal and t for transverse). The phonon transmission coefficient [17, 31] from Material 1 to Material 2,  $\alpha_{1-2}$ , can be written as

$$\alpha_{1-2} = \frac{\sum_{j} v_{2,j}^{-2}}{\sum_{j} v_{1,j}^{-2} + \sum_{j} v_{2,j}^{-2}},$$

(6)

and  $v_D$  is the speed of sound calculated using the Debye model:

$$v_D = \left(v_l^{-3} + 2v_t^{-3}\right)^{-1/3}. (7)$$

The DMM estimate can lead to substantial deviations in the thermal interface conductance near room temperature because the Debye approximation does not properly account for the complexity of the phonon dispersion relationships at the edge of the Brillouin zone [30, 32]. Depending on the material combination and temperature, Reddy et al. [30] reported as large as 100 percent difference between the Debye model and a numerical computation considering the full dispersion relationship over the entire Brillouin zone. There is some evidence that the presence of at least one amorphous material can mitigate the error due to the strong scattering of short wavelength phonons – for which dispersion is most important – in the amorphous The determination of the error is further complicated by the material [29, 33]. polycrystalline structure of molybdenum on the opposite side, which may render the use of an average, isotropic dispersion relationship more appropriate. For these reasons, Chapter 5 of the present work models the phonon transport across a metalamorphous semiconductor interfaces using the DMM with Debye approximation. Further research on the crystalline-amorphous interfaces considering the full dispersion relationship on one side and strong scattering on the other would be useful in refining the modeling developed in the present work.

Figure 3. Illustration of the two-temperature model (TTM). Temperatures of the electron system ( $T_e$ ) and the phonon system ( $T_p$ ) in the metal side deviates from each other near the metal-dielectric interface. Thermal energy carried by the electrons must first be transferred to the phonons in the metal layer before being carried to the dielectric side by the phonons.

The DMM only models the phonon transport across a material interface. However, metal-dielectric or metal-semiconductor interfaces are common in a variety of nanodevices [21, 32, 34-36]. Since the electron concentration in dielectrics and most semiconductors is negligible, for thermal transport across the interface, electrons in the metal need to transfer their energy into the phonon system in the metal before the phonons can carry the heat across the metal-dielectric or metal-semiconductor interface (Figure 3). This electron-phonon nonequilibrium can be modeled by the two-temperature model (TTM) [22, 24, 37]. The TTM states that the electron temperature and phonon temperature deviate from each other near the metal-dielectric interface where the electrons and phonon are not in equilibrium. It extends the heat diffusion equation with an electron-phonon interaction term:

$$k_e \frac{\partial^2 T_e}{\partial z^2} - G(T_e - T_p) = 0; \quad k_p \frac{\partial^2 T_p}{\partial z^2} + G(T_e - T_p) = 0, \tag{8}$$

where the subscript e and p denotes electrons and phonons, respectively. The parameter G is an electron-phonon coupling factor which describes the rate of energy exchange between the electron system and the phonon system in the metal. Assuming the metal film is thick enough such that the  $T_e$  and  $T_p$  converge at locations far away from the interface (see Figure 3), the additional thermal resistance due to the electron-phonon nonequilibrium process,  $R_{ep}$ , can be derived as [22]

$$R_{ep} = \frac{1}{\sqrt{Gk_{p,metal}}} \tag{9}$$

where  $k_{p,\text{metal}}$  is the phonon contribution of the thermal conductivity of the metal. Chapter 5 provides detailed discussion of the TTM in the context of the heat conduction through Mo/Si multilayers.

For a metal-dielectric interface, the electrons may also exchange energy with the phonon system in the dielectric by scattering inelastically at the interface. Although ignored in some of the previous work on ultrathin metal/dielectric multilayers [32, 34, 35], the inelastic electron-interface scattering may be significant if the metal film thickness is close to or less than the electron mean free path [37-39]. Past research has used the inelastic phonon radiation limit theory [40], the maximum transmission model [41], the anharmonic inelastic model [42], and a quasi-analytical approach combined with experimental data [43, 44] to quantify the inelastic thermal conductance. The modeling work presented in Chapter 5 considers this inelastic scattering effect and discusses its relative strength and impact on the overall thermal resistance of a metal/dielectric multilayer.

# 1.3 Electrical Techniques for Thermal Measurement

Thermal characterization techniques are essential to better understanding of thermal phenomena at the nanoscale. Thin film materials play an important role in advanced nanodevices owing to their unique mechanical, thermal, and electrical properties. Nanostructured materials usually exhibit reduced thermal conductivities as compared to bulk materials because of more frequent scattering of energy carriers at material interfaces, material impurities, grain boundaries, and lattice defects. The film geometry, grain structures, and phase impurities can also render the thermal conductivity of thin films anisotropic, meaning that the thermal conductivity in the inplane direction is different from the out-of-plane value [25, 26]. The thermal boundary resistance (TBR) has been shown to be a significant, sometimes the dominant, contributor to the overall thermal resistance of nanostructures [20]. One experimental challenge is to accurately measure the anisotropic thermal properties of the nanometer-scale thin films and separating out the effect of TBR. This work develops a set of electrical thermometry techniques, useful for measuring the thermal conductivity anisotropy, and makes progress towards improving the thermal metrology for nanostructured materials and interfaces.

## 1.3.1 The $3\omega$ Technique

One widely used electrical thermometry method for characterizing thermal conductivity is the  $3\omega$  technique, which was first introduced by Cahill and colleagues [45, 46]. This method uses the harmonic Joule heating of a microfabricated metal bridge to extract the thermal properties of the underlying materials. The schematic of a typical  $3\omega$  sample is shown in Figure 4(a). The metal bridge is usually fabricated with widths ranging from tens of micrometers to tens of nanometers, depending on specific applications and lithography resolution. The four-probe configuration facilitates accurate resistance measurement because it minimizes the impact of electrical contract resistance between the contact pads and the probe tip. The film of interest, typically with thickness from tens of nanometers to a few micrometers in this work, is deposited on top of a substrate. Depending on the electrical conductivity of the thin film, passivation layers may be required on the top and bottom of the thin film to avoid electrical leakage.

Figure 4. Schematic of a typical setup for  $3\omega$  measurements. (a) schematic of a sample structure. Metal bridges with a 4-probe configuration are fabricated on top of the thin film. Passivation layers (not shown) may be necessary between the metal pattern and the thin film, as well as between the thin film and the substrate. (b) a typical measurement circuit using differential amplifiers. The sample and a variable resistor are denoted as  $R_x$  and  $R_y$ , respectively.

Figure 4 (b) shows the schematic of a typical circuit for  $3\omega$  measurement. A current source generates an ac current at frequency  $\omega$  that runs through the metal bridge on the sample and a variable resistor connected in series. Joule heating within the metal bridge induces the temperature of the metal heater bridge to oscillate at frequency  $2\omega$ . The variable resistor is selected to have a much lower temperature

coefficient of resistivity (TCR), so that most of the resistance change is contributed by the metal bridge. The change in resistance is captured by monitoring the voltage drop across the sample  $(R_x)$  and the variable resistor  $(R_v)$  by differential amplifiers. Due to the linear relationship between temperature and the electrical resistivity of the metal bridge, the measured voltage contains a smaller, third harmonic  $(3\omega)$  component in addition to the larger, fundamental  $(\omega)$  component. The variable resistor is fine tuned to the same resistance as the metal bridge, so that the voltage oscillation at  $\omega$  can be cancelled out by a third differential amplifier. A lock-in amplifier captures the amplitude and phase information of the remaining  $3\omega$  signal, which are functions of the thermal properties of the underlying layer. Chapter 2 presents the detailed experimental procedure and data reduction method used in this work.

The  $3\omega$  technique has been further developed over the past decade to extend its capability in thermal characterization of complex thin film systems. D. Cahill and colleagues [45, 46] in their original  $3\omega$  experiment measured the thermal conductivities of bulk materials including SiO<sub>2</sub>, Pyrex, nitrate glass, and PMMA. T. Yamane et al. [47] used a used a Wheatstone bridge-based  $3\omega$  circuit to measure the thermal conductivity of SiO<sub>2</sub> films deposited by different processes with thickness from a few tens of nanometers to 1 µm. B. Olson et al. [48] developed an data reduction method to extend the  $3\omega$  method for multilayer structures. In addition to the focus on the  $3\omega$  component, C. Dames et al. [41] showed the usefulness of the other two components (1 $\omega$  and 2 $\omega$ ) in extracting the thermal properties and improved the flexibility of the  $3\omega$  technique. Many thin film materials have been characterized by the  $3\omega$  technique for a variety of applications: D. Borca-Tasciuc et al. [49] measured the specific heat and thermal conductivity of multi-wall carbon nanotube (CNT) strands, D.-W. Oh et al. [50] applied the  $3\omega$  technique to aluminum oxide nanofluids, and more recently W. Risk et al. and R. Fallica et al. [51-53] studied the thermal properties of the phase change chalcogenide Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> for memory applications.

The metrology techniques developed in this work further advance the  $3\omega$  measurement, by suspending the thin film [25, 26] and developing nanoscale heater bridges with varying width, in order to characterize two-dimensional thermal

characterization [21]. Chapter 2 and Chapter 5 provide detailed discussions on these measurements.

### 1.3.2 Steady-State Joule Heating Thermometry

Many modern nanodevices usually contain thin films of different materials stacked together to form a multilayer structure. The thermal properties of each constituent film, which are located at different depth below the top surface, are important in engineering the thermal performance of the nanodevice. Frequency-domain thermometry such as the  $3\omega$  technique can probe different depths into the underlying layers by varying the frequency of the driving current. On the other hand, heat confinement can also be achieved by steady-state Joule heating by varying the width of the heaters. This spatial heat confinement provides a convenient way to probe thermal properties at different depths within a film, as well as to characterize the thermal resistance of the entire multilayer structure for a range of length scales.

The schematic of the dc Joule heating measurement sample is shown in Figure 5. When dc electrical current runs through the metal heat bridge, the temperature rises due to the Joule heating. Because the electrical conductivity of the metal typically decreases linearly with temperature for the temperature range of this work, the electrical resistance of the heater bridge changes with temperature as

$$R(T) = R_0 \left( 1 + \alpha \Delta T \right) \tag{10}$$

where R(T) and  $R_0$  are the electrical resistances of the heater bridge at temperature T and at a reference temperature. The temperature coefficient of resistivity (TCR)  $\alpha$  is a material property and considered constant, and  $\Delta T$  denotes the temperature rise from the reference temperature. By measuring the electrical resistance change of the metal heater bridge, one can derive the temperature rise of the heater bridge with Eq. (10). The thermal resistance  $R_{th}$  that this heater experiences is by definition:

$$R_{th} = \frac{\Delta T}{Q},\tag{11}$$

where Q is the amount of Joule heating power that was dissipated through the multilayer stack. For small temperature rises, it is safe to ignore the convective and radiative heat loss at the top surface and assume that all the Joule heating power goes into the multilayer structure.

Figure 5. Schematic of a multilayer structure and heater bridges with varying widths. Narrow heaters confine the heat within a shallow region below the surface, and their temperature rise is not sensitive to the thermal properties of the layers further below. The heat generated from the wide heaters probes deeper into the multilayer stack. Schematic is not drawn to scale.

Heaters with varying widths probe into different regions of the underlying layers by means of spatial heat confinement. Heat generated from narrow heaters (compared to the layer thickness) sees the underlying structure as a semi-infinite medium, and most of the temperature drop is confined within a small region underneath the narrow heater. This spatial heat confinement provides a way to measure the thermal conductivity of the very thin layers near the top because the temperature rise of the heater is highly sensitive to the thermal properties of the material in this shallow region, and less sensitive to the materials further down (for example, the substrate). The narrow heaters are also useful in measuring the in-plane thermal conductivity because of the significant two-dimensional heat spreading from the heater line. Wider heaters, on the other hand, generate almost one-dimensional heat flow through the top

layers of the sample and, thus, are less sensitive to the in-plane thermal conductivity of this shallow region. The heat generated from the wider heaters can penetrate deep into the multilayer stack, and the temperature drop from the layers to the substrate can be significant. Therefore, the temperature rise of the wide heaters is more sensitive to the thermal properties of the layers near the bottom and the TBR at each interface.

The steady-state Joule heating thermometry has been widely used to for thermal characterization of thin-film materials and other nanostructured devices. W. Liu *et al.* measured the thermal properties of single-crystal silicon-on-insulator (SOI) layers down to approximately 20 nm [54]. P. Kim *et al.* observed a thermal conductivity of more than 3000 W/mK of individual multiwall carbon nanotubes by fitting the steady-state Joule heat data to a theoretical model [55]. E. Pop *et al.* applied dc DC Joule heating power to a single wall carbon nanotube with a diameter of 1.7 nm and measured a thermal conductivity of nearly 3500 W/mK [56, 57]. More recently, S. LeBlanc *et al.* measured the thermal conductivity of zinc oxide nanowires for energy conversion applications [58], and A. Marconnet *et al.* studied periodically porous silicon nanobridge for photonic applications using a similar steady-state Joule heating approach [59].

Furthermore, the steady-state Joule heating thermometry provides a convenient way to study the thermal resistance of nanostructured electronic devices at different length scales. Modern nanodevices often feature a hierarchy of characteristic length scales. For example, a high electron mobility transistor (HEMT) usually consists of local hotspots in the individual channels with dimensions of approximately 1  $\mu$ m, a multigate array with dimensions of 10-100  $\mu$ m, and the device package level of above 1000  $\mu$ m. Effective thermal management requires knowledge of the thermal resistances that are experienced by these different length scales, as well as the dominating factor that contributes to the overall thermal resistance. Heater bridges with varying widths can accurately measure the thermal resistances for different length scales and, in conjunction with thermal modeling, identify the specific layers or TBRs that are critical to the temperature rise of the nanodevice. Chapter 3 describes the

detailed steady-state Joule heating measurement and modeling approach in the context of HEMT applications.

## 1.3.3 Suspended Structures for In-Plane Measurements

The thermal conduction in the in-plane direction has been of increasing interest over the past decade. Measurement of the heat conduction in the in-plane direction is important for a variety of microdevices with lateral structures. For example, M. Lankhorst *et al.* fabricated a low-current phase change memory (PCM) device with a Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> bridge connecting the two electrodes laterally [60], and Y. Yin *et al.* developed a TiN/SbTeN double layer in the in-plane direction to achieve multibit programming in PCM [61, 62]. The few-layer graphene heat spreader, developed by Z. Yan *et al.* [63], effectively removes heat from localized hot spots in high-power GaN transistors and redistributes it laterally to the nearby heat sinks. Thermal properties of the relevant compounds and thin films can exhibit strong anisotropy, and accurate in-plane thermal characterization is important in the successful design of these nanodevices.

Figure 6. Temperature distribution of on-substrate and suspended structures. Top: schematics of the sample structures. Middle: numerical simulation of the temperature distributions. Bottom: temperature profile at the top surface in the lateral direction from the center of the heater to the edge of the sample (heat sink). (a) On-substrate structures usually show limited sensitivity to the in-plane conduction when the heater is much wider than the thickness of the thin film. (b) Suspended structures force all the heat to dissipate laterally and are therefore highly sensitive to the in-plane thermal conductivity of the thin film.

Conventional on-substrate structures for thermal characterization typically feature a metal heater to generate heating power, a thin film or multilayer of interest, and a silicon substrate. The high thermal conductivity of silicon makes it an effective heat sink drawing most of the heat vertically through the thin film as shown in Figure 6. This effect is most significant when the film thickness is much smaller than the heater

width, which is usually limited by the photolithography resolution (~1 µm). The suspended structure, on the other hand, can force the heat generated from the metal heater to dissipate laterally along the thin film before reaching the heat sinks at the edge. The temperature profile, which is nearly linear assuming convection and radiation heat loss can be neglected, is highly sensitive to the in-plane thermal conductivity and can be accurately measured by metal bridges deposited on the suspended thin film [64] or by Raman thermometry [65]. A frequency-domain measurement with the suspended structure can also resolve the thermal diffusivity and heat capacity of the thin film material [66].

Many variations of the suspended structures have been developed to characterize the thermal properties of a variety of nanomaterials and nanostructures. X. Zhang *et al.* measured the thermal conductivity and thermal diffusivity of silicon nitride film of 0.6 μm and 1.4 μm using the electrical thermometry with the suspended structure. W. Cai *et al.* [65] and A. Balandin *et al.* [67] fabricated single suspended layers of graphene and measured their in-plane thermal conductivity to be around 2000–5000 W/mK. The concept of suspended structures is also applicable to the thermal characterization of other non-planar nanostructures. Recent research has fabricated and measured the thermal conductivities of the free-standing structures including carbon nanotubes [56, 57, 68], zinc oxide, nickel, and silicon nanowires [58, 69-71], and DNA strands [72]. The design and fabrication of suspended structures to measure the in-plane thermal conductivity and heat capacity of Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> thin films are discussed in Chapter 2.

#### 1.4 Thesis Overview

This work addresses thermal transport phenomena in nanostructured materials and devices. In particular, this work develops a set of electrothermal characterization techniques and theoretical modeling approaches and applies them to three nanodevices and nanostructures: phase change memory (PCM), gallium nitride high electron

mobility transistors (HEMT), and molybdenum/silicon multilayers for extreme ultraviolet (EUV) mirrors.

Chapter 2 starts with the measurements of in- and out-of-plane thermal conductivities of Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> thin films for PCM. The work presents the detailed experimental design and methodology of the 3ω technique and suspended measurement structures. Grain structure characterization of the Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> film facilitates the understanding and modeling of the thermal conductivity anisotropy in the thin film. Coupled electrothermal simulations predict the impact of the anisotropic thermal conduction on the performance of PCM devices.

The discussion of PCM continues in Chapter 3 which focuses on multibit programming capability. A set of coupled electrical, thermal, and phase transitional models describes the crystallization process in the nanodevice under transient electrothermal conditions. The simulations evaluate two standard PCM structures, the mushroom cell and the confined pillar cell, with feature sizes smaller than 40 nm. This work also explores a more compact architecture, the stacked vertical cell, with precise control of the Joule heating and potentially more stable intermediate resistance levels.

Chapter 4 is devoted to the discussion of thermal phenomena in HEMT devices. This work starts by reviewing the recent thermal data of the relevant materials and interfaces for GaN-based HEMT devices. Steady-state Joule heating thermometry, with nanoheaters with widths down to 50 nm, measures the thermal conductivity of the constituent materials of a HEMT structure with a diamond substrate for improved thermal management. A numerical code calculates the temperature rise of the multilayer structure and reveals the individual contribution of different layers to the overall thermal resistance at three distinct characteristic length scales: the single gate hot spot, the multigate array, and the device package.

Chapter 5 applies the  $3\omega$  technique with the nanoheaters with varying widths to measure the anisotropic thermal conductivity of Mo/Si multilayers for EUV lithography applications. This chapter also develops a theoretical model for the phonon-electron energy conversion at and near the metal/semiconductor interfaces.

This work introduces a criterion for the transition from electron to phonon dominated heat conduction in metal films bounded by dielectrics.

Chapter 6 concludes the dissertation by summarizing the major contributions of this work and suggesting future work which extends the understanding of heat transfer in nanomaterials and nanodevices.

# Chapter 2: Anisotropic Thermal Conduction in Phase Change Memory

### 2.1 Introduction

Phase change memory (PCM) is becoming promising for next-generation nonvolatile memory applications due to its high read/write speeds, improved reliability and superior scalability [1, 3]. PCM stores information by exploiting the difference in electrical resistivity between crystalline and amorphous phases of the phase change material. The reversible phase transformations are induced through intense local Joule heating caused by electrical current pulses.